TYPE

340

PRECISION

INCREMENTAL

CRT DISPLAY

TYPE

340

PRECISION

INCREMENTAL

CRT DISPLAY

COPY NO. 55

This manual contains proprietary information. It is provided to the customers of Digital Equipment Corporation to help them properly use and maintain DEC equipment. Revealing the contents to any person or organization for any other purpose is prohibited.

#### INTRODUCTION

This manual is one of a series of documents needed for understanding, operating, and maintaining the Type 340 Precision Incremental CRT Display. The maintenance manual for the computer used is the primary supporting document, as it contains specific information on the operation of the computer, a generalized instruction list, a treatise on maintenance, an explanation of the operation of each type of module used in the computer, logical block diagrams and schematics of all the circuits in the computer, and an explanation of the logical symbology used in the drawings.

An important subsidiary document is the Digital System Modules Catalog, C-100. This publication contains operating descriptions and logical diagrams of many of the modules used in the computer and display, as well as explanations of the voltage and timing characteristics of standard signals, examples of various applications which aid in understanding the equipment, and an explanation of Digital logical symbology.

A series of MAINDEC program tapes and manuals are included in the supporting documentation. A MAINDEC program tape is a punched paper tape containing a series of maintenance programs that exercise various parts of the equipment. These exercises are designed to localize or specify the cause of any failure in various portions of the equipment. A MAINDEC manual contains a description of the associated program tests, operating instructions, flow diagrams, and a listing of the programs on the tape. These manuals are listed in Section 4, Maintenance.

The remainder of the supporting documentation consists of the maintenance manuals provided by other manufacturers for their items, such as special power supplies, which are used in the computer and display.

# CONTENTS

| Section |                             | Page |

|---------|-----------------------------|------|

| 1       | DESCRIPTION                 | 1-1  |

|         | Physical Description        | 1-3  |

| 2       | PROGRAMMING                 | 2-1  |

|         | 340 Instruction Format      | 2-2  |

|         | Parameter Mode (000)        | 2-2  |

|         | Point Mode (001)            | 2-3  |

|         | Slave Mode (010)            | 2-4  |

|         | Character Mode (011)        | 2-5  |

|         | Vector Mode (100)           | 2-5  |

|         | Vector Continue Mode (101)  | 2-6  |

|         | Increment Mode (110)        | 2-6  |

|         | Subroutine Mode (111)       | 2-7  |

|         | PDP-1 Programming           | 2-9  |

|         | PDP-4 and PDP-7 Programming | 2-11 |

|         | PDP-6 Programming           | 2-13 |

| 3       | LOGICAL OPERATION           | 3-1  |

|         | Signal Flow                 | 3-1  |

|         | Initial Starting            | 3-1  |

|         | Parameter Mode              | 3-2  |

|         | Point Mode                  | 3-4  |

|         | Vector Mode                 | 3-6  |

|         | Vector Continue Mode        | 3-7  |

|         | Increment Mode              | 3-8  |

|         | Character Mode              | 3-11 |

|         | Subroutine Mode             | 3-12 |

|         | Slave Mode                  | 3-13 |

|         | Circuit Operation           | 3-13 |

|         | Initializing                | 3-14 |

## **CONTENTS** (continued)

| Section |                                    | Page |

|---------|------------------------------------|------|

|         | Transferring                       | 3-15 |

|         | Storing                            | 3-18 |

|         | Deflecting                         | 3-22 |

|         | Repeating                          | 3-25 |

|         | Vector Generating                  | 3-28 |

|         | Incrementing                       | 3-31 |

|         | Character Byte Selecting           | 3-34 |

|         | Move Circuit                       | 3-35 |

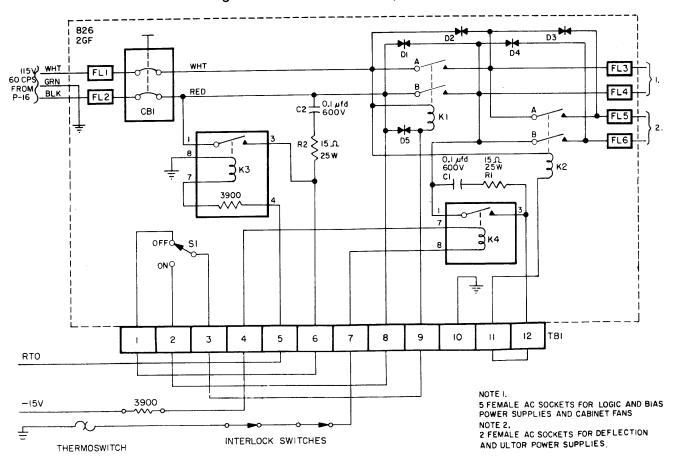

|         | AC Power Control and Distribution  | 3-36 |

|         | Special Module Circuit Description | 3-36 |

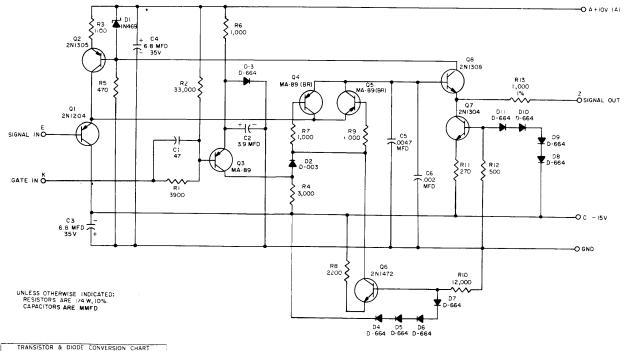

|         | Type 1567 Display Preamplifier     | 3-36 |

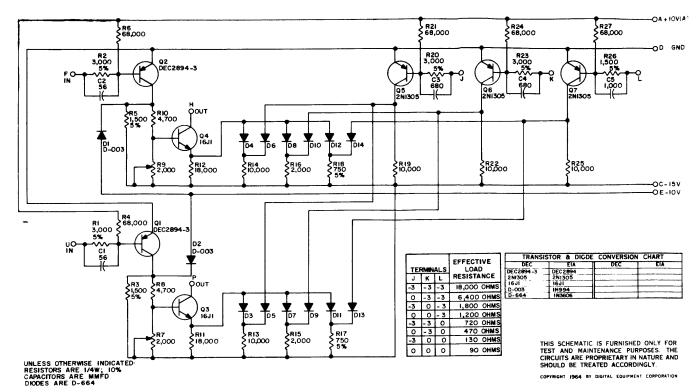

|         | Type 1575 Follow or Hold Circuit   | 3-38 |

|         | Type 1579 Feed Forward             | 3-40 |

| 4       | MAINTENANCE                        | 4-1  |

|         | Preventive Maintenance             | 4-3  |

|         | Mechanical Checks                  | 4-4  |

|         | Power Supply Checks                | 4-5  |

|         | Marginal Checks                    | 4-7  |

|         | Corrective Maintenance             | 4-10 |

|         | Preliminary Investigation          | 4-11 |

|         | System Troubleshooting             | 4-11 |

|         | Circuit Troubleshooting            | 4-12 |

|         | Repair                             | 4-16 |

|         | Validation Test                    | 4-17 |

|         | Log Entry                          | 4-18 |

|         | Assembly and Disassembly           | 4-18 |

|         | Logic Modules                      | 4-18 |

|         | Power Supplies                     | 4-18 |

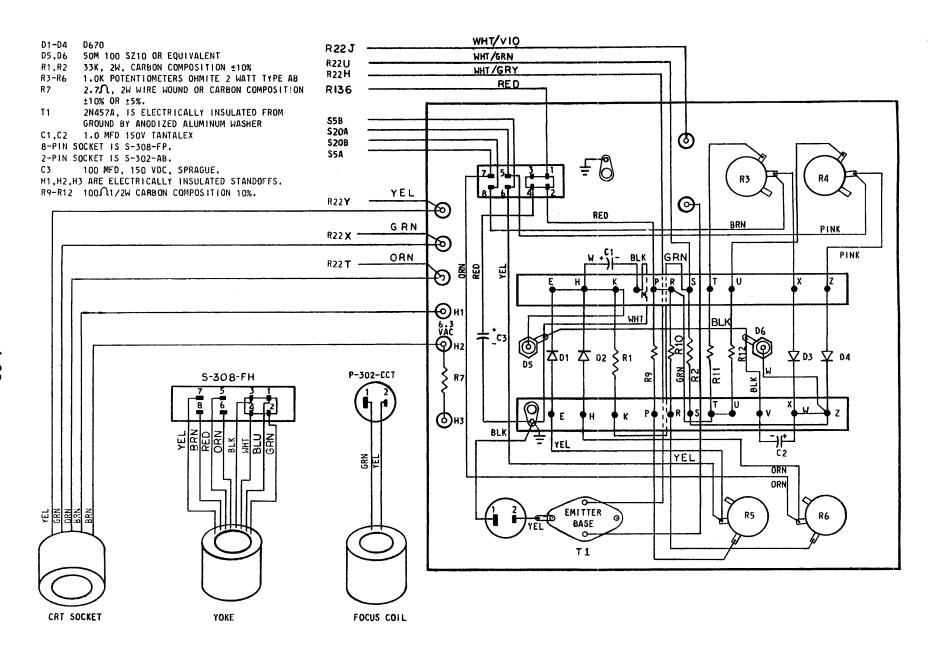

|         | Deflection Output Amplifier        | 4-19 |

# CONTENTS (continued)

| Section |                                | Page |

|---------|--------------------------------|------|

|         | Cathode Ray Tube               | 4-19 |

|         | Coil Assembly                  | 4-22 |

|         | Ad justments                   | 4-24 |

|         | Centering Magnet Adjustment    | 4-24 |

|         | Coil Adjustment                | 4-25 |

|         | Focus                          | 4-26 |

|         | Raster Position                | 4-26 |

|         | Raster Size                    | 4-27 |

|         | Common Mode Current            | 4-28 |

|         | Brightness                     | 4-29 |

|         | Straightness                   | 4-29 |

|         | Deflection Speedup             | 4-33 |

|         | Delay Time                     | 4-36 |

|         | Repeatability                  | 4-37 |

|         | Spare Parts                    | 4-38 |

| 5       | INSTALLATION                   | 5-1  |

|         | Site Requirements              | 5-1  |

|         | Physical Requirements          | 5-1  |

|         | Electrical Requirements        | 5-2  |

|         | Installing                     | 5-4  |

| 6       | ENGINEERING DRAWINGS           | 6-1  |

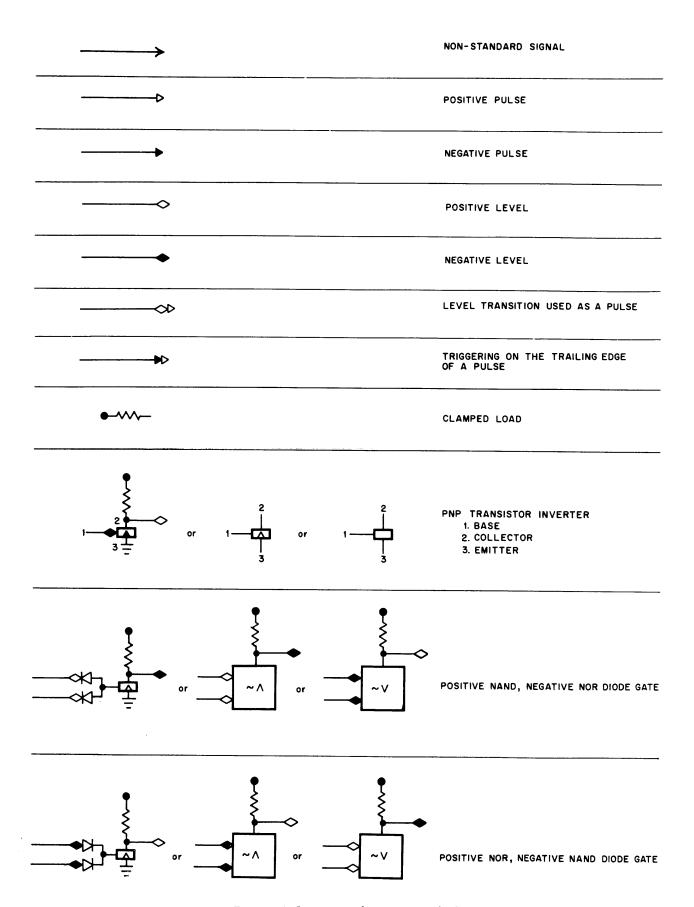

|         | Logic Signals                  | 6-1  |

|         | ILLUSTRATIONS                  |      |

| Figure  |                                |      |

| 1-1     | Type 340 Layout and Dimensions | 1-5  |

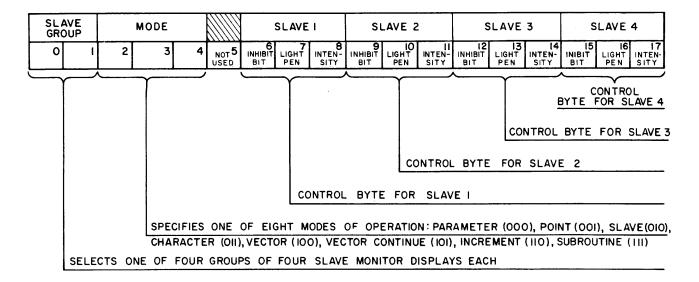

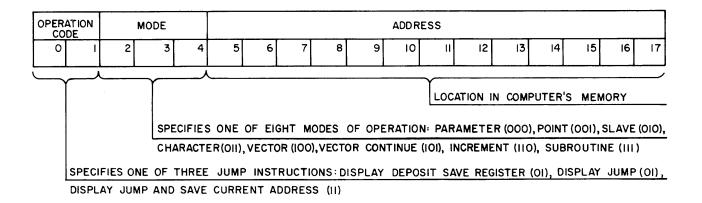

| 2-1     | Parameter Mode Bit Format      | 2-2  |

| 2-2     | Point Mode Bit Format          | 2-3  |

## ILLUSTRATIONS (continued)

| Figure |                                                                  | Page |

|--------|------------------------------------------------------------------|------|

| 2-3    | Slave Mode Bit Format                                            | 2-4  |

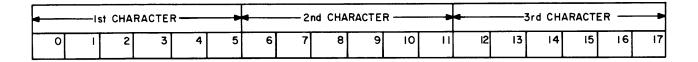

| 2-4    | Character Mode Bit Format                                        | 2-5  |

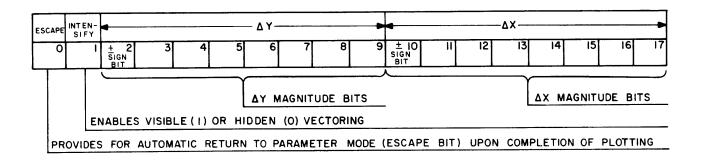

| 2-5    | Vector and Vector Continue Modes Bit Format                      | 2-6  |

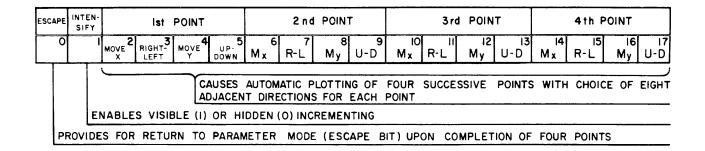

| 2-6    | Increment Mode Bit Format                                        | 2-7  |

| 2-7    | Subroutine Mode Bit Format                                       | 2-7  |

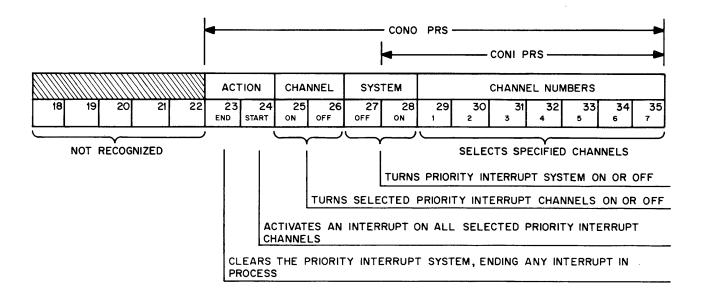

| 2-8    | Priority Interrupt System Bit Format                             | 2-13 |

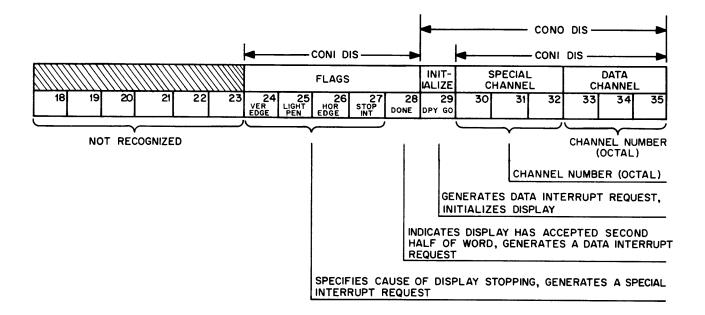

| 2-9    | Display Interface Conditions Bit Format                          | 2-14 |

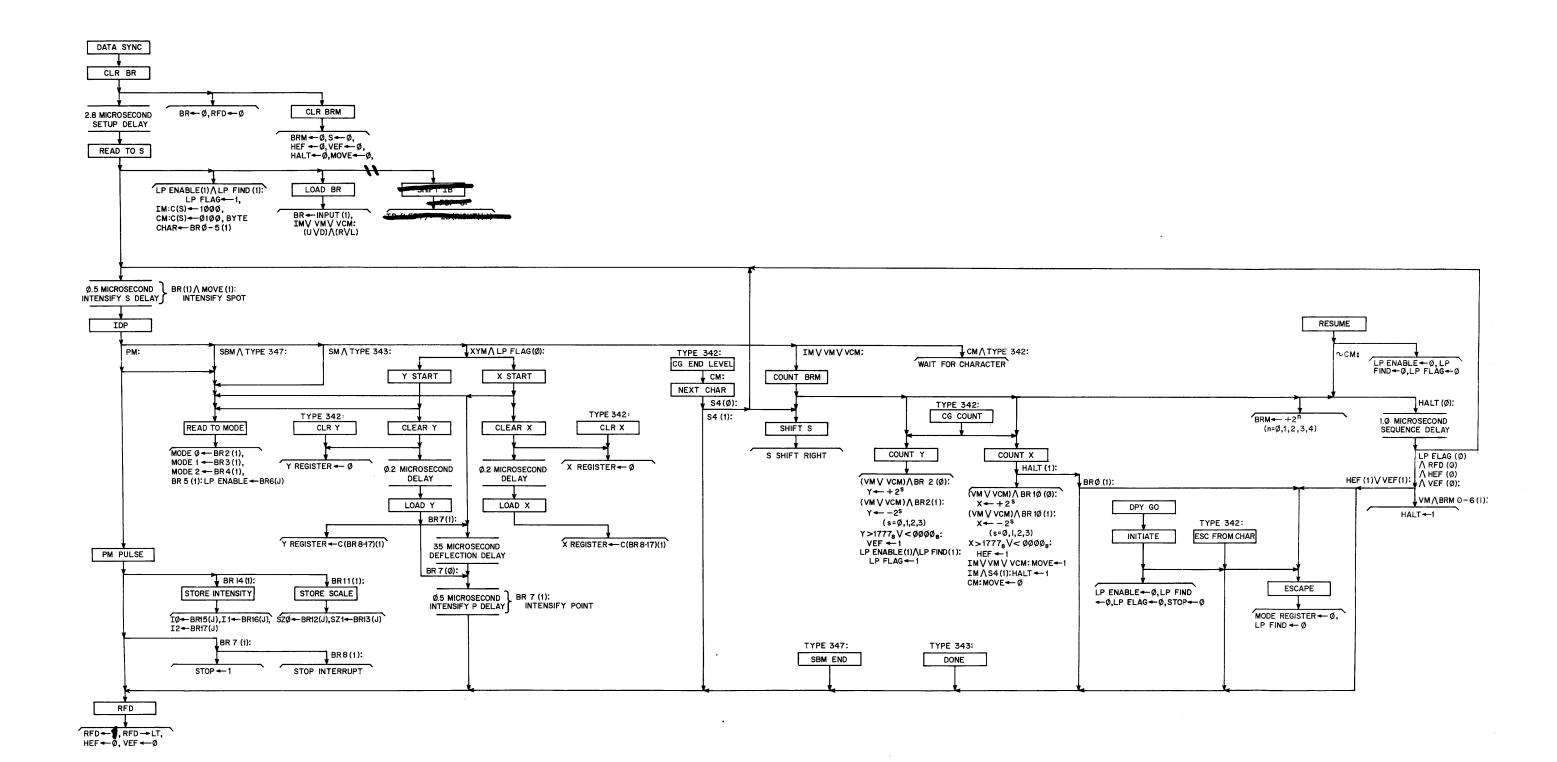

| 3-1    | Type 340 Signal Flow Diagram                                     | 3-3  |

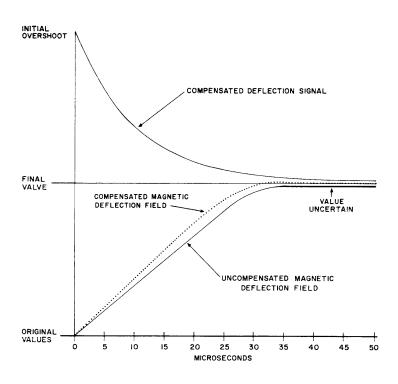

| 3–2    | Deflection Compensation Characteristics                          | 3-25 |

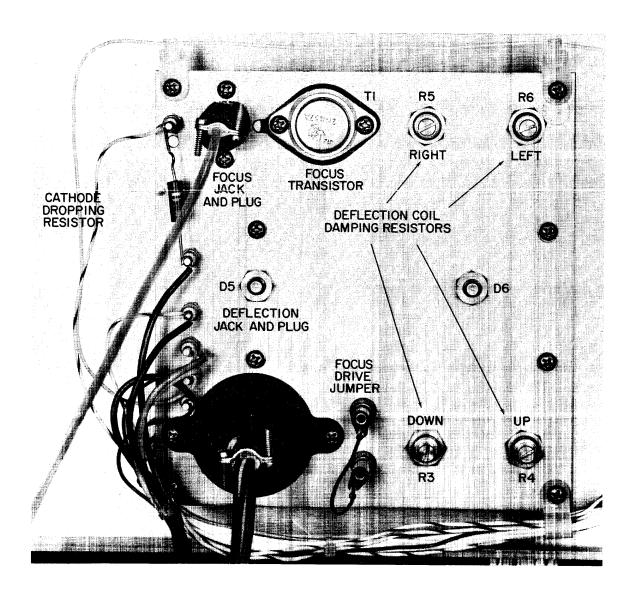

| 4-1    | Component Mounting Plate                                         | 4-20 |

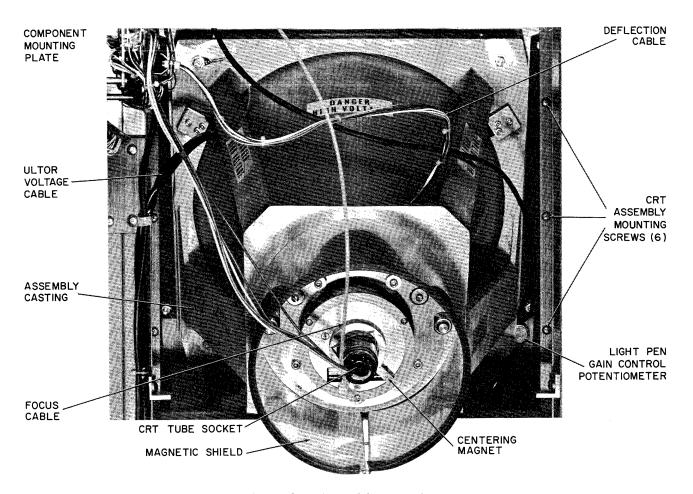

| 4-2    | CRT Assembly in Cabinet                                          | 4-21 |

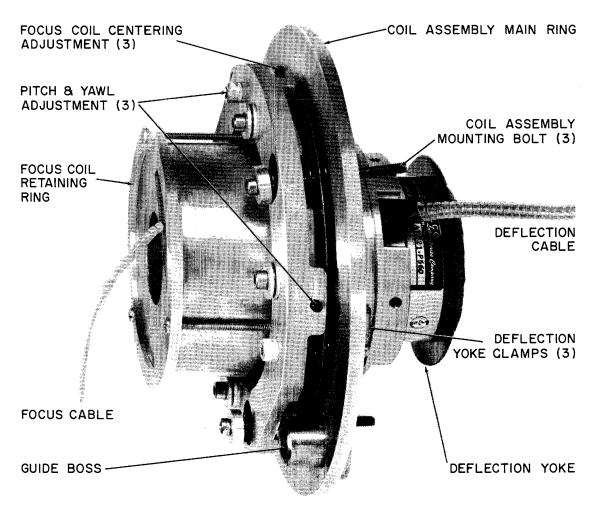

| 4-3    | Coil Assembly Components                                         | 4-23 |

| 4-4    | Type 1567 Adjustment Locations                                   | 4-27 |

| 4-5    | Type 1568 Adjustment Locations                                   | 4-32 |

| 4-6    | Feed Forward Waveform Adjustments                                | 4-34 |

| 4-7    | Type 1579 Adjustment Locations                                   | 4-36 |

| 6-1    | Digital Logic Symbols                                            | 6-2  |

| 6-2    | Digital Cable and Component Numbering                            | 6-5  |

| 6-3    | Type 340 Block Diagram                                           | 6-7  |

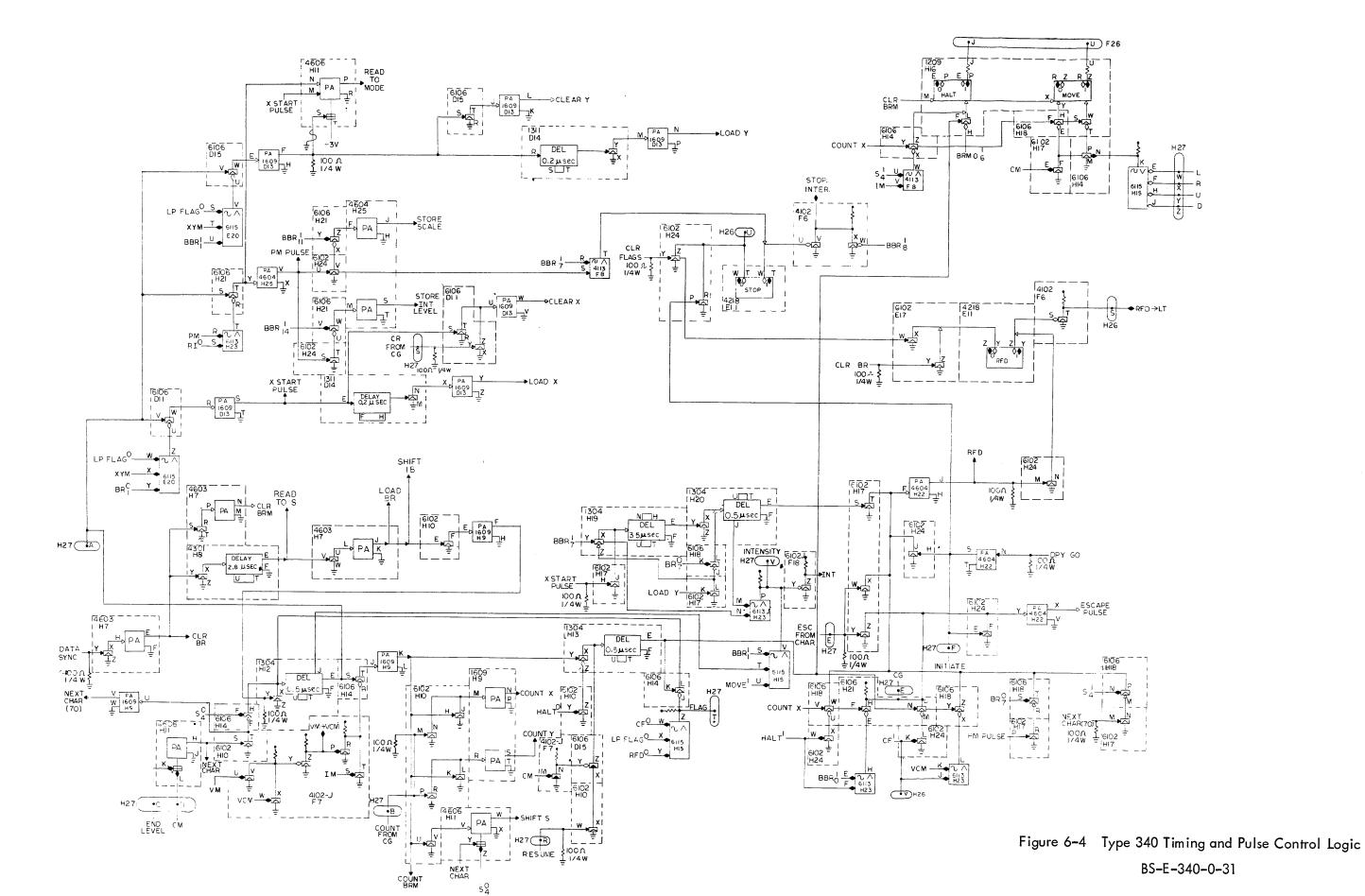

| 6-4    | Type 340 Timing and Pulse Control Logic, BS-E-340-0-31           | 6-9  |

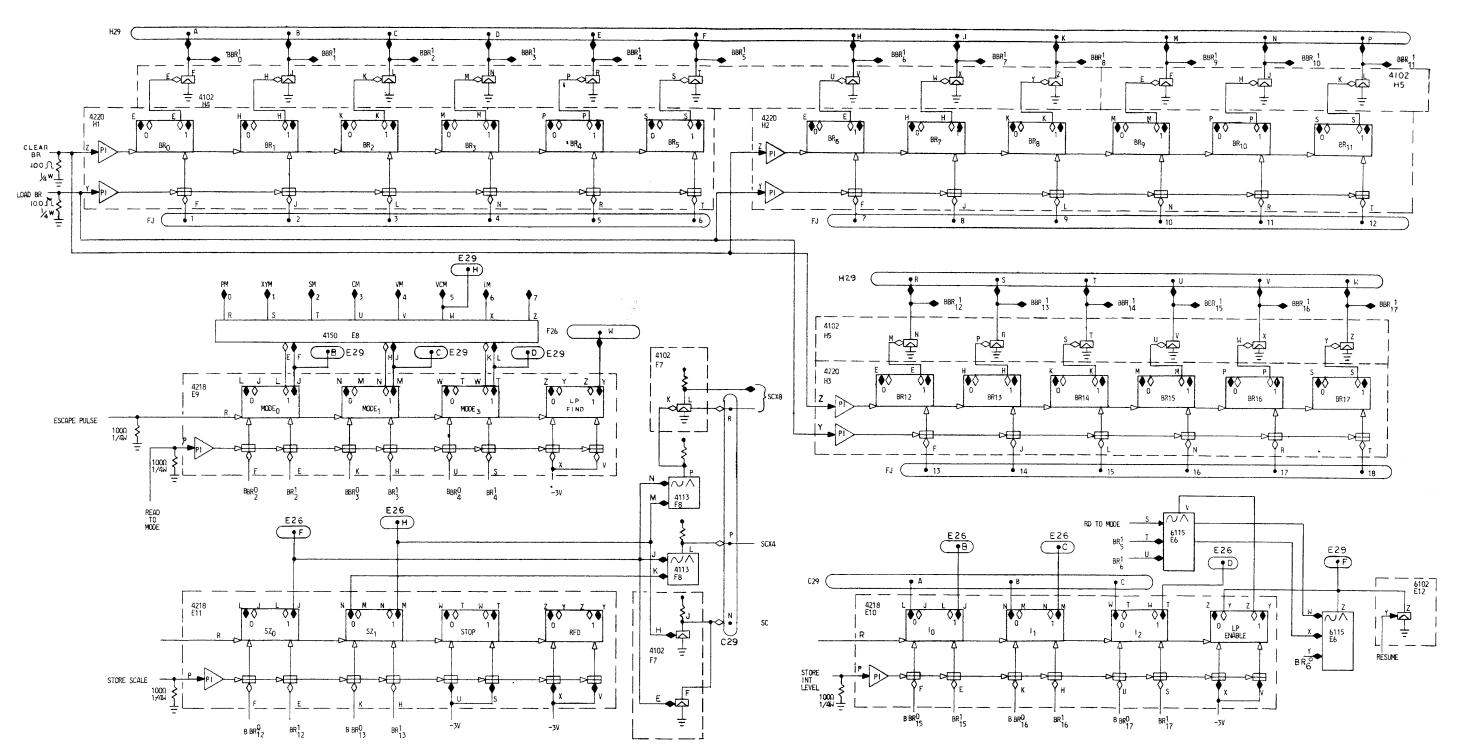

| 6-5    | Type 340 Input Register and Parameter Store Logic, BS-D-340-0-28 | 6-11 |

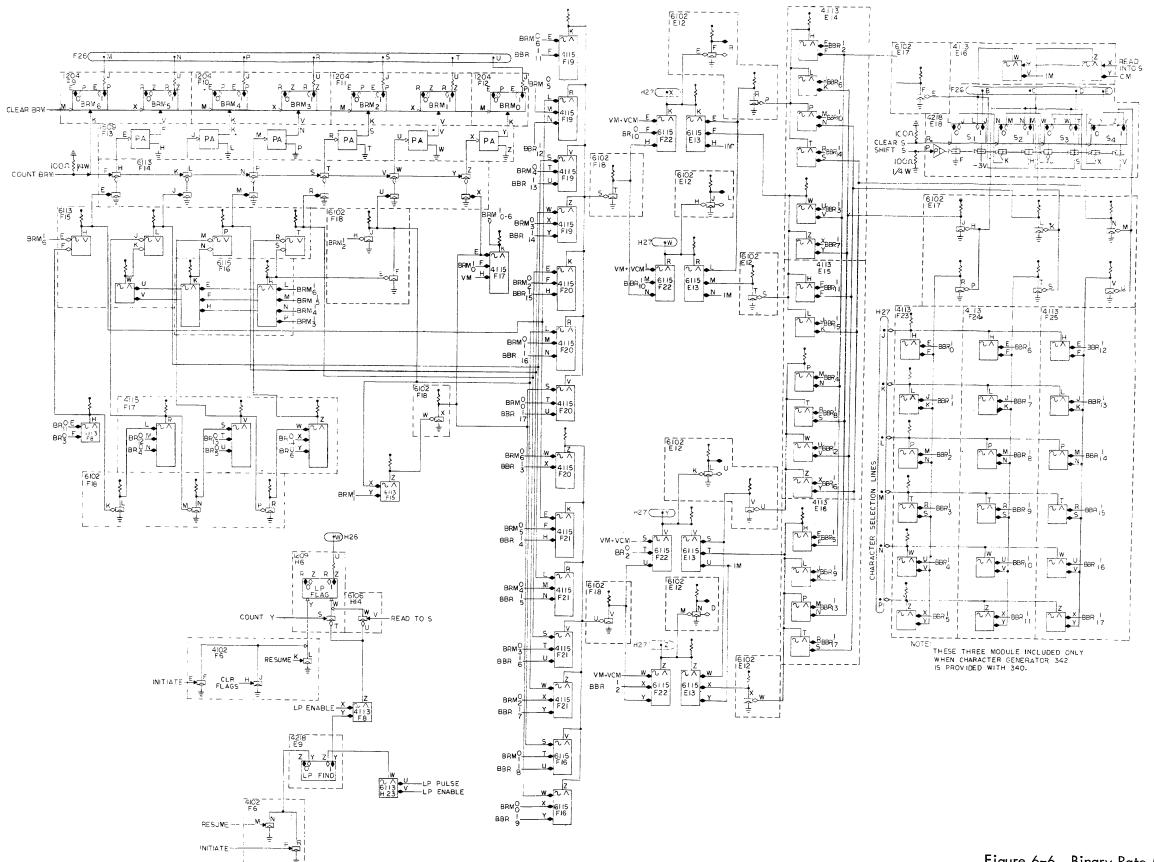

| 6-6    | Binary Rate Multiplier and Increment Logic, BS-E-340-0-29        | 6-13 |

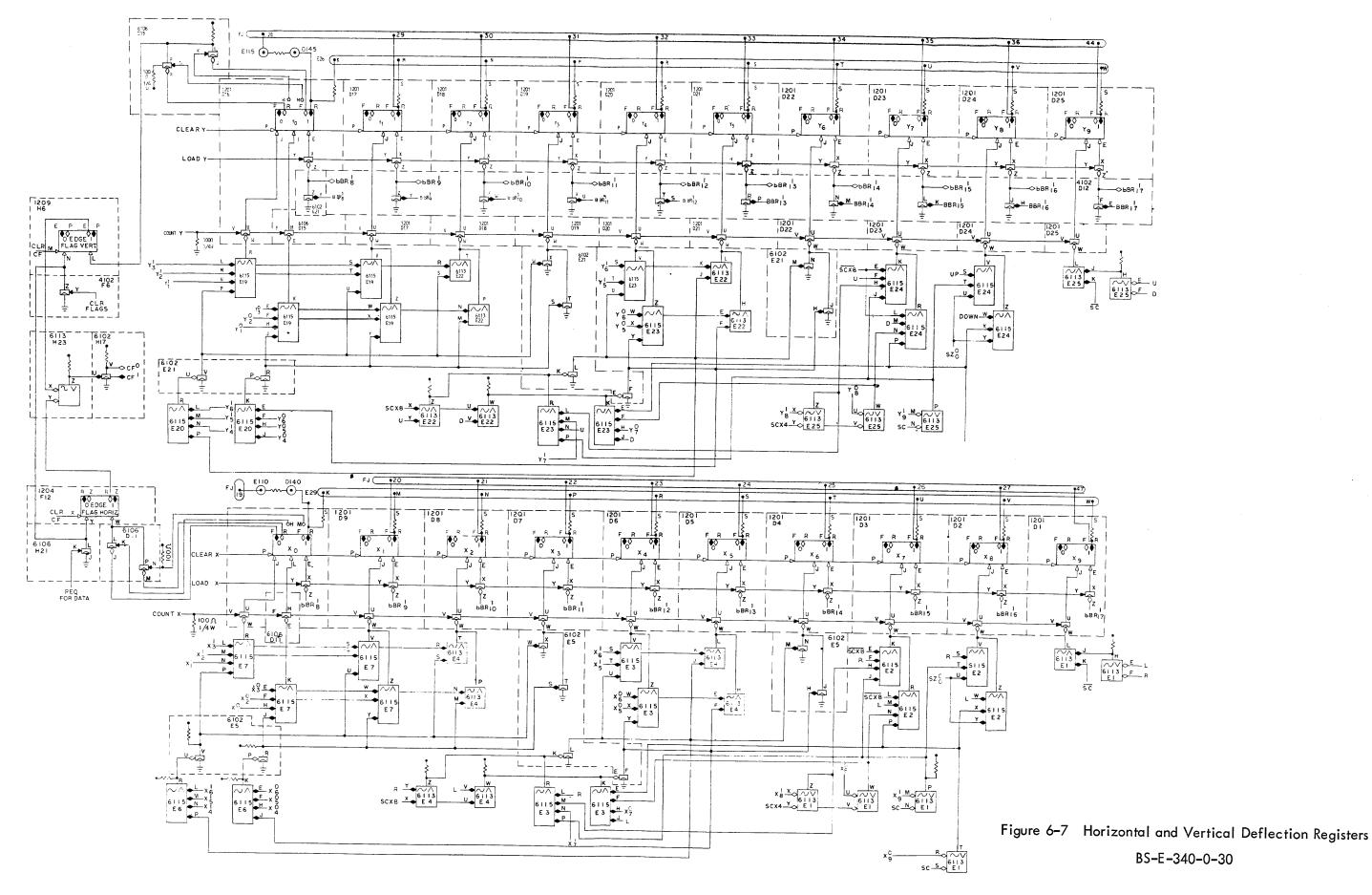

| 6-7    | Horizontal and Vertical Deflection Registers, BS-E-340-0-30      | 6-15 |

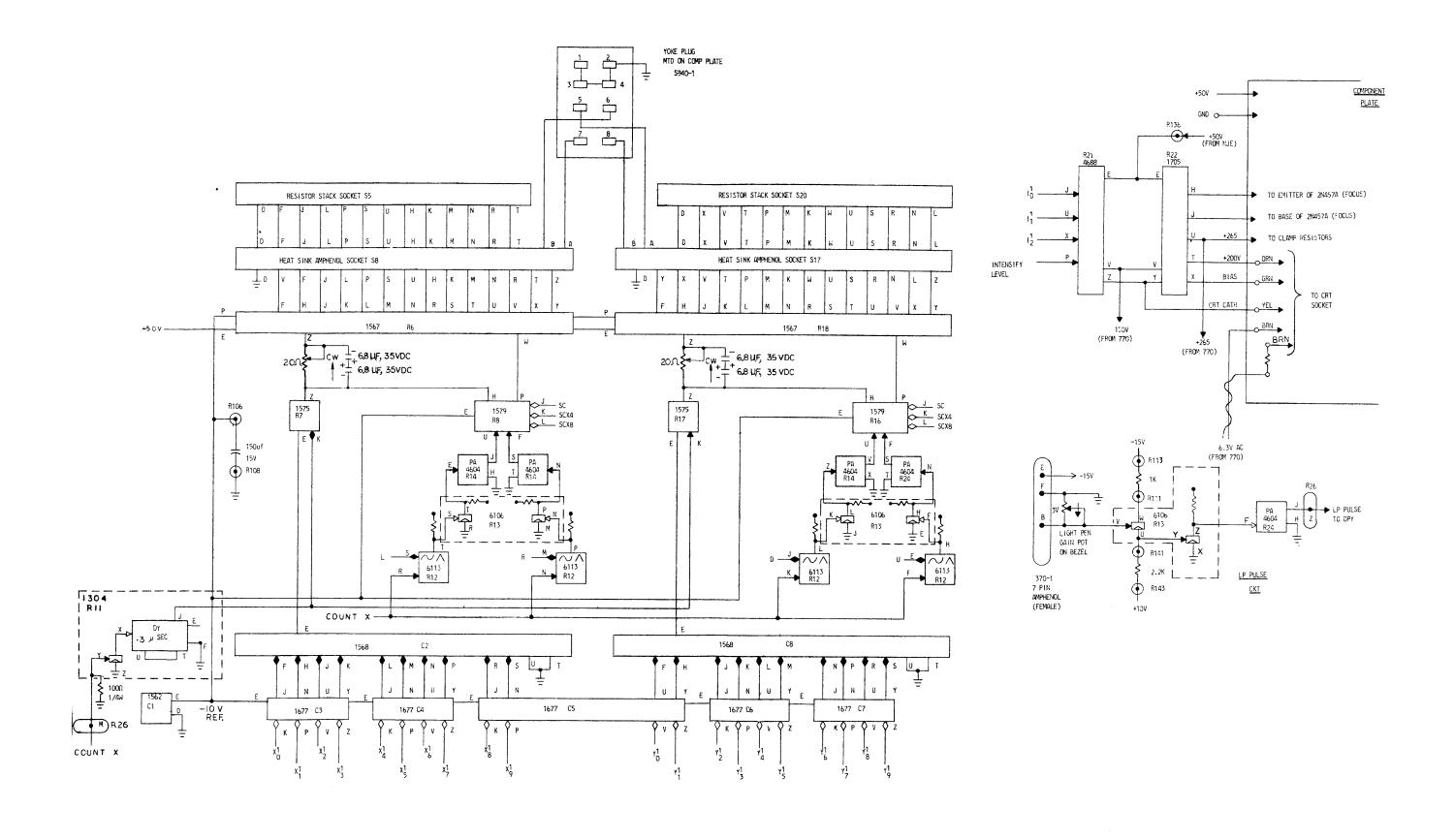

| 6-8    | Type 340 Deflection Logic, BS-D-340-0-27                         | 6-17 |

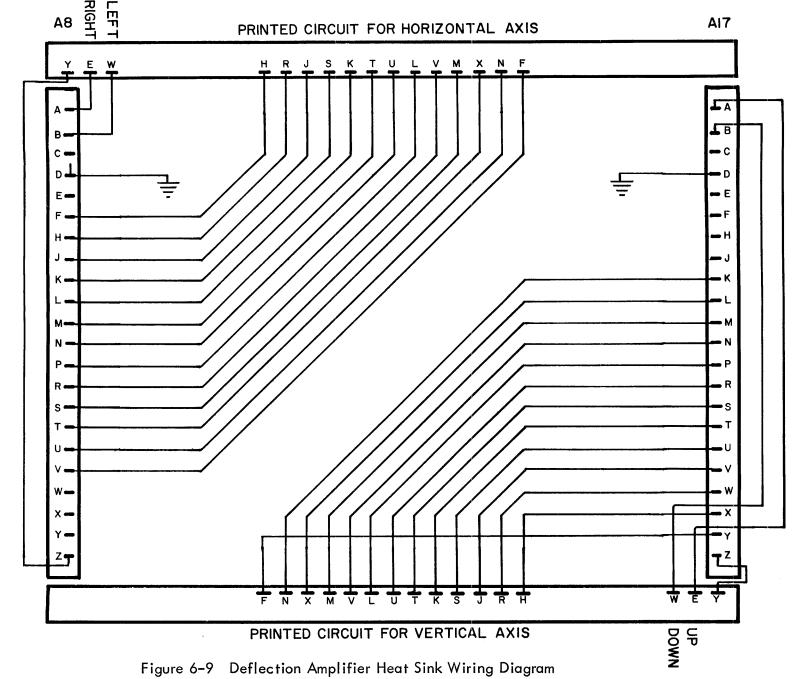

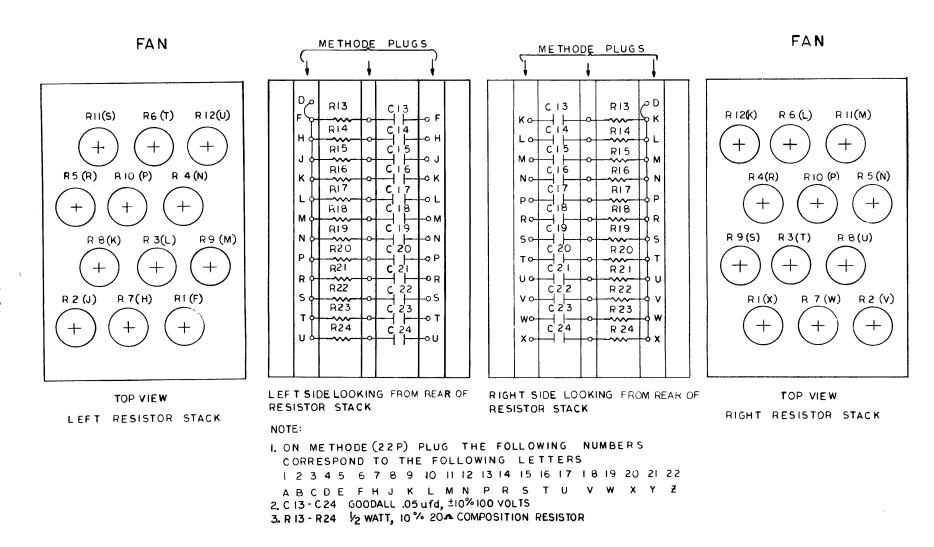

| 6-9    | Deflection Amplifier Heat Sink Wiring Diagram, WD-B-22106        | 6-19 |

| 6-10   | Deflection Amplifier Resistor Stack Wiring Diagram, WD-C-22106   | 6-20 |

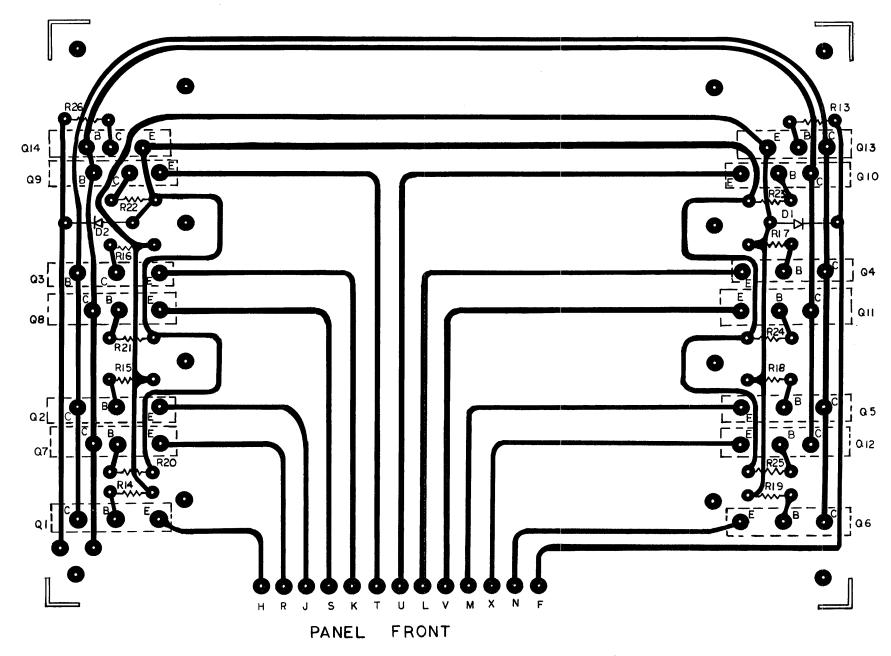

| 6-11   | Deflection Amplifier Printed Circuit Layout, MA-B-22116          | 6-21 |

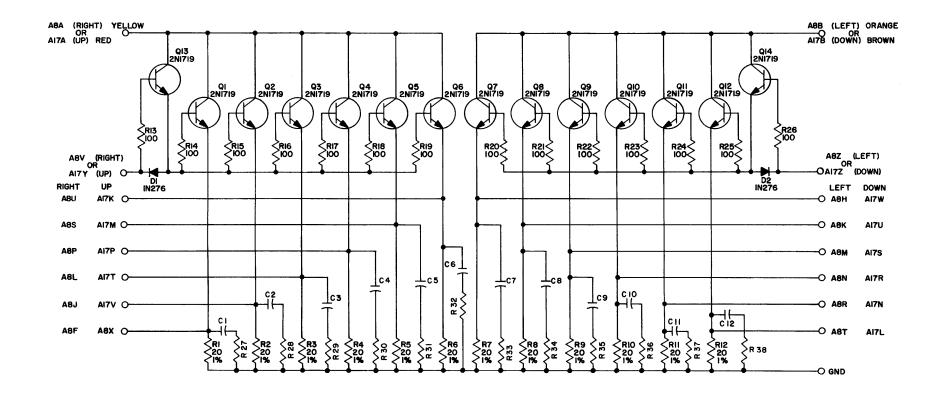

| 6-12   | Deflection Output Amplifier Schematic, CS-B-22100                | 6-22 |

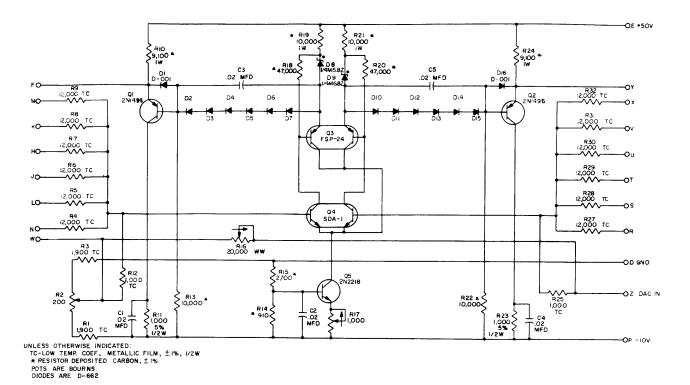

| 6-13   | Display Preamplifier, CS-1567                                    | 6-23 |

| 6-14   | Follow or Hold, CS-1575                                          | 6-23 |

# ILLUSTRATIONS (continued)

| Figure |                                               | Page |

|--------|-----------------------------------------------|------|

| 6-15   | Feed Forward, CS-1579                         | 6-24 |

| 6-16   | Type 826 Power Control                        | 6-24 |

|        | TABLES                                        |      |

| Table  |                                               |      |

| 1-1    | Type 340 Physical Specifications              | 1-4  |

| 1-2    | Type 340 Operating Specifications             | 1-6  |

| 2-1    | Typical PDP-1 IOT Display Instructions        | 2-10 |

| 2-2    | PDP-4 and PDP-7 Display IOT's                 | 2-12 |

| 2-3    | Typical PDP-6 Programming Examples            | 2-17 |

| 3-1    | Increment Mode Operation                      | 3-9  |

| 3-2    | Scale Level Relationships                     | 3-21 |

| 3-3    | Vector Generator Comparisons                  | 3-31 |

| 4-1    | Maintenance Equipment                         | 4-1  |

| 4-2    | Maintenance Controls and Indicators           | 4-2  |

| 4-3    | Power Supply Outputs                          | 4-6  |

| 4-4    | 10-Bit Digital-To-Analog Converter Adjustment | 4-31 |

| 4-5    | Spare Parts Provisioning                      | 4-38 |

| 4-6    | Other Modules Used in Display                 | 4-39 |

| 5-1    | Interface Signals at FJ                       | 5-3  |

| 5.2    | Interface Signals at H27                      | 5-4  |

Type 340 Precision Incremental CRT Display

### SECTION 1

#### DESCRIPTION

The Type 340 Precision Incremental CRT Display was specifically designed for use by the Programmed Data Processors -1, -4, -6, and -7 made by the Digital Equipment Corporation, but it may be used by any digital computer. The display receives a word of digital data from the computer, interprets the word as control or data information, automatically performs the required operations, and signals the computer when it is finished. Information can be displayed as either single random-position dots, straight lines, curved lines, or characters. Only logic levels are used in communicating between the display and the computer, making the operation of the display asynchronous with the computer. The digital word which contains the control and data information is 18 bits long. This word is loaded into a storage buffer register within 3 microseconds after the computer supplies a pulse or level with a fast (0.2 microsecond) rise time. The computer is then free for other operations, and may load another word into the display anytime after the display generates a level indicating it has completed its operation.

With the addition of the direct access channel option the Type 340 is uniquely suited to operate as a small computer. The direct access channel contains an indexable address register that provides direct access to the computer memory without disturbing the main computer operation. The computer loads the starting address of a block in memory into this register and initiates a display operation. Each time the display completes an operation, it breaks the computer program for one cycle while it fetches the word specified by this address register and loads it into the buffer register. The address register is then indexed by one, so it points to the next word in the block, much as a program counter does. The block in memory therefore acts as a subroutine program for the display. This series of operations terminates when a word with the stop bit set is received. The display then signals the computer that it has finished its operation.

Communication between the user and the computer can be increased by using the Type 370 Light Pen option. The light pen is a fast-response photosensitive device that produces a pulse and sets a flag when it sees any single spot displayed during the 0.5-microsecond intensification time. By this means the computer can be signaled to perform some preprogrammed function at a specific time and/or location.

The Type 340 is capable of eight modes of operation. Each word contains information that specifies the mode of operation for the next succeeding word and operation. These modes are:

- (1) PARAMETER MODE When the display has been set to the parameter mode, it interprets the next word as containing information that may change its present mode, scale, intensity, light pen control, and interruption control parameters.

- (2) POINT MODE When the display has been set to the point mode, it interprets the next word as containing a coordinate location and information that may change its present mode, light pen, and intensify control parameters.

- (3) VECTOR MODE When the display has been set to the vector mode, it interprets the next word as containing the vector size and direction information, as well as intensify control and escape information. The display remains in the vector mode until the escape bit is set, at which time it reverts to the parameter mode. If the edge of the raster is violated, a flag is set and the display returns to the parameter mode.

- (4) VECTOR CONTINUE MODE When the display has been set to the vector continue mode, it interprets each succeeding word as containing direction information of a vector from the starting point to the edge of the raster, as well as intensify control and escape information. In this respect it is similar to the vector mode. When the vector violates the edge of the raster, the display returns to the parameter mode.

- (5) INCREMENT MODE When the display has been set to the increment mode, it interprets each succeeding word as containing information to move the spot to four successive locations, each adjacent to the preceding spot. The spot can be placed into any one of the eight adjacent locations at each movement. The word also contains intensify control and escape information. The display remains in the increment mode until the escape bit is set, at which time it returns to the parameter mode.

- (6) CHARACTER MODE The display only operates in the character mode when it is equipped with the Type 342 Character Generator option. In this mode, the display interprets each succeeding word as containing three alphanumeric characters or other symbols, each specified by six bits. The display remains in the character mode until a special code is encountered, at which time it reverts to the parameter mode.

- (7) SUBROUTINE MODE The display only operates in the subroutine mode when it is equipped with the Type 347 Subroutine Interface option. When set to this mode, the display interprets the next word as a jump instruction to some different location in memory. The subroutine word also sets the mode for the next word to be transferred. Three different jump instructions are decoded and implemented by the Type 347.

- (8) SLAVE MODE The display only operates in the slave mode when it is equipped with the Type 343 Monitor option. When set to the slave mode, the display interprets the next word as a control word for up to four individual slave monitor displays in one of four different slave groups. This word turns on or off the intensity circuits and light pens of the particular slave on command. Up to 16 slaves can be used to monitor all or any part of the presentation of the main display. The slave word also sets the mode for the next word to be transferred.

#### PHYSICAL DESCRIPTION

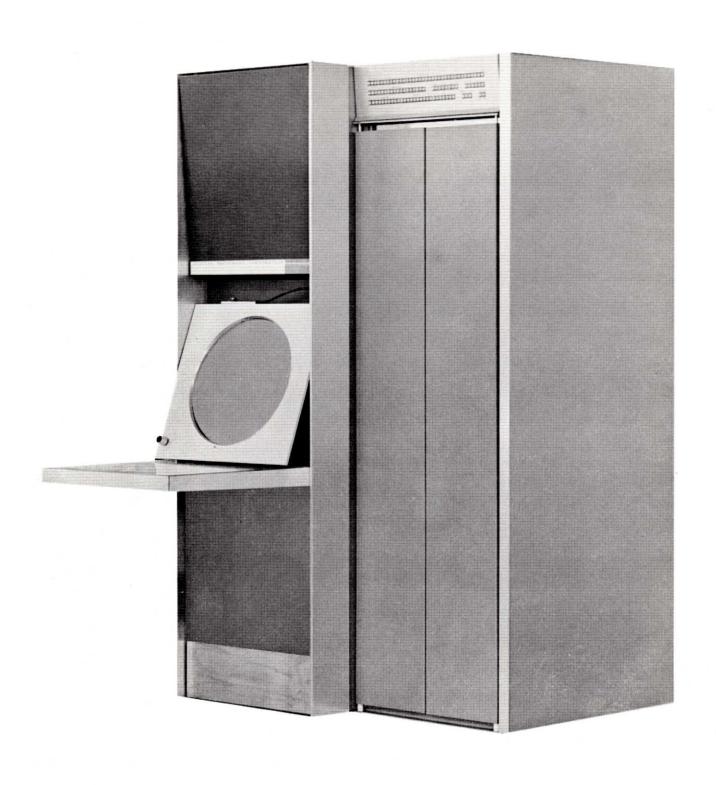

The 340 is housed in two vertical equipment bays, as shown in the frontispiece. The bays are connected together and supported by eight castered rollers. The display can be easily moved about within the area dictated by the 50 foot cables to the computer and ac power receptacle.

The cathode ray tube, its deflection circuits, and special power supplies are mounted in the left-hand bay. The CRT is located in the center of the bay and is inclined 30° to provide the best working angle. A small table top projects out beneath the CRT mounting panel for the convenience of the user.

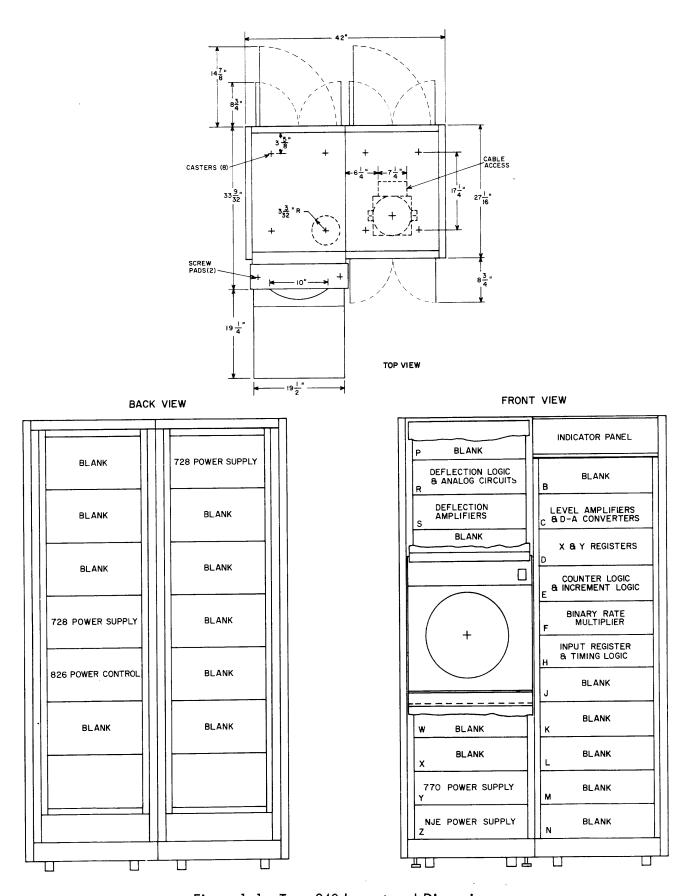

All the logical circuits which control the display are located in the right-hand bay, along with their indicators and power supplies. The indicators are located at the top of the bay, above the double doors in front. The logical circuits are located in racks behind these doors. The power supplies are mounted on a plenum door in the rear of the bay, behind a pair of swinging doors. Figure 1-1 shows the physical shape and equipment layout of the display.

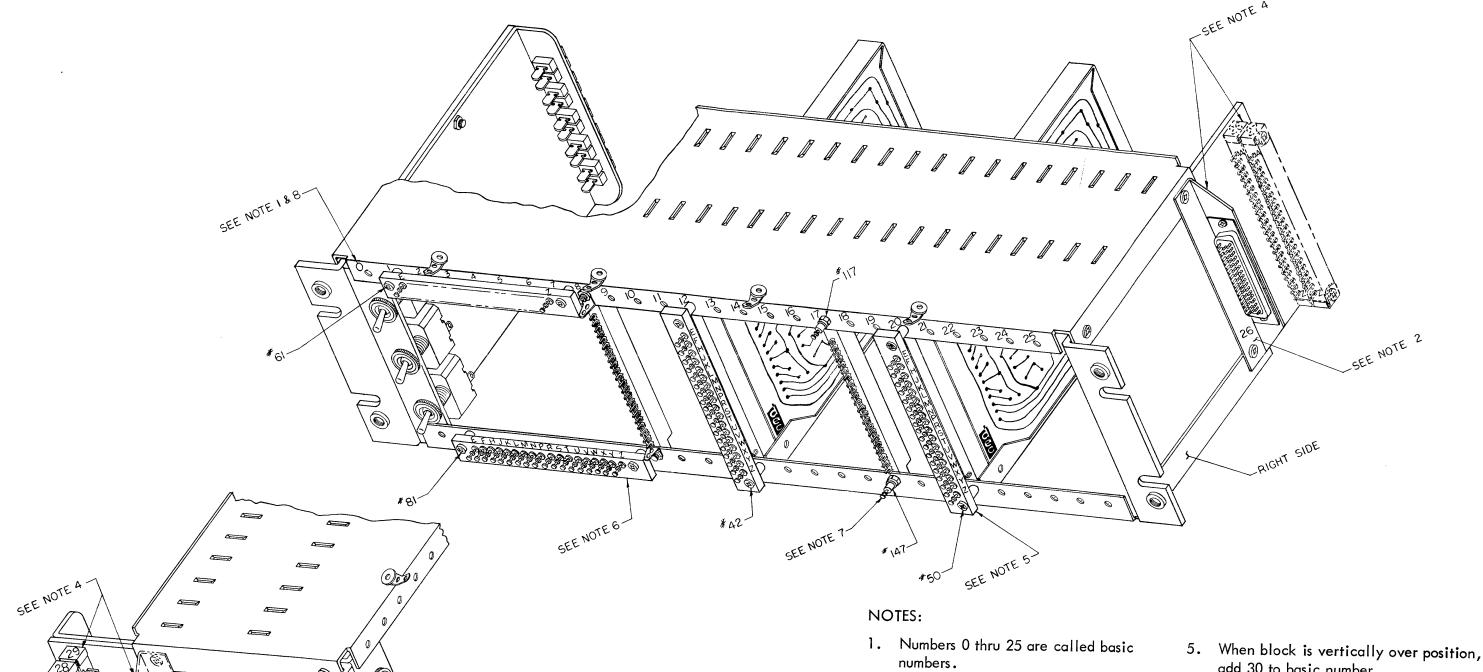

The system modules which make up the logical control circuits plug into sockets mounted on a rack. Each rack is identified by a letter indicating the location of the rack in the display. These letters are combined with the socket number to specify a particular module. For example, E09 specifies the ninth module from the left (when looking at the front, or wiring side, of the rack) in rack E (fifth from the top) of bay 1.

Each rack socket and module plug contain 22 terminals, identified by the letters of the alphabet (G, I, O, and Q are not used), starting at the top. All terminals are therefore identified by adding the terminal letter as a suffix to the module location code. An example is E09Z, the last terminal of the previous module location example.

Cable receptacles and the corresponding plugs are designated with the same system of bay number and rack designation, with the numbers 26 through 29 added as a suffix. If the number is 26 or 27, the socket is located on the right side of the rack at the rear, while the numbers 28 or 29 are for the corresponding location on the left side. Terminal boards and standoff terminals are also numbered in a similar fashion, as shown in Figure 6-1.

TABLE 1-1 TYPE 340 PHYSICAL SPECIFICATIONS

| Dimensions | 42 inches wide, 51 inches deep (with table), 69-1/8 inches high, 27-1/2 inches table top height.                                                                    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Weight     | Approximately 700 pounds, supported on eight castered rollers and two screw pads.                                                                                   |

| Housing    | Two vertical DEC cabinets, one with an extension on the front. Paint is blue, with off-white table and charcoal brown accent panel. Anodized brushed aluminum trim. |

Figure 1-1 Type 340 Layout and Dimensions

TABLE 1-1 TYPE 340 PHYSICAL SPECIFICATIONS (continued)

| Clearance    | Three feet of access room is required at the rear for maintenance. Two feet is recommended on the left side.                         |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Controls     | The light pen gain control located at the lower left of the front panel is the only operating control.                               |

| Display Tube | Fixed mount in center of left bay. The tube is tilted 30°. A 1/8-inch sheet of form-fitted plexiglass protects the face of the tube. |

TABLE 1-2 TYPE 340 OPERATING SPECIFICATIONS

| THE TENTE OF CHANGE OF CONTRACTOR |                                                                                                                                 |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| Input Power                       | $115\pm10$ volts, 60 cycle single phase, at 13 amps (20 amps surge). 50 cycle and/or 220- to 250-volt power supplies available. |  |

| Power and Heat<br>Dissipation     | 1.5 kilowatts, 4950 Btu/hour.                                                                                                   |  |

| Ambient Temperature               | 50°F (10°C) to 110°F (43°C).                                                                                                    |  |

| Cathode Ray Tube                  | 16ADP7A. Radius of curvature 40 inches.                                                                                         |  |

| Raster Size                       | 9-3/8 inches by $9-3/8$ inches, containing 1,024 points by 1,024 points.                                                        |  |

| Pincushion Distortion             | Less than 3/32 inch per side.                                                                                                   |  |

| Deflection and Focus              | Magnetic.                                                                                                                       |  |

| Spot Size                         | Approximately 0.030 inch, 0.015 inch at the half-light output points.                                                           |  |

| Address Scheme                    | 2's complement, with (0,0) located at the lower left-hand corner of the raster.                                                 |  |

| Stability                         | $\pm0.05$ inch in 8 hours at a nearly constant temperature (± 3°F).                                                             |  |

| Repeatability                     | $\pm0.05$ inch regardless of the location of the previous spot.                                                                 |  |

TABLE 1-2 TYPE 340 OPERATING SPECIFICATIONS (continued)

| Timing          | 3 microseconds for information transfer, 35 microseconds per point for random positioning, 1.5 microseconds per point in the vector, vector continue, increment, and character modes. |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modes           | Parameter, point, vector, vector continue, increment, and character.                                                                                                                  |

| Intensification | Preset at 0.5 microseconds per point.                                                                                                                                                 |

| Indicators      | The current state of the coordinate registers and all control flip-flops is shown by indicator lights at the top of the right-hand bay.                                               |

### SECTION 2

#### PROGRAMMING

The Type 340 is controlled completely by the computer to which it is attached. The programming of this computer and display combination varies for almost all installations because of the differences in the computers and the different options used with the display. This section discusses some of the general aspects of writing programs for the display and lists many of the instructions used by the PDP-1, PDP-4, PDP-7, and the PDP-6.

Of primary importance, when writing a display program, is the manner in which the 18-bit word is transferred to the display. In most cases, this word contains information which is the result of some previous operation and therefore is stored in the memory of the computer. In the simplest type of installation, this word must be retrieved from memory and placed into the computer output register by one instruction and then transferred to the display by another instruction. The display then operates on this word and signals the computer when it has finished, at which time the computer must repeat the transfer process. This causes frequent and time-consuming interruptions of the main program of the computer.

This disadvantage can be relieved with the use of the direct access channel, an option with the PDP-1 and standard with the PDP-4 and PDP-7. The required information words are loaded into a table, or block of successive memory locations, and the beginning location of this table is loaded into a special register called the display address counter (DAC). The output of the DAC is applied directly to the inputs of the memory address (MA) register. A data break is then initiated by either the display or the computer, and this address is read into the MA. The computer then goes through a break cycle in which it fetches the word from memory and places it into its memory buffer (MB) register from where it is transferred directly to the buffer register (BR) in the display. During this time, the display starts its operation and the DAC is incremented by one. The computer program counter (PC) is not incremented during the break cycle. At the end of the break cycle the computer continues its main program until the display requires another data break.

#### 340 INSTRUCTION FORMAT

The 18-bit word which is transferred to the 340 is interpreted differently in each mode of operation. Each mode requires that the information in the word follow a definite format. These formats are described in the following section.

### Parameter Mode (000)

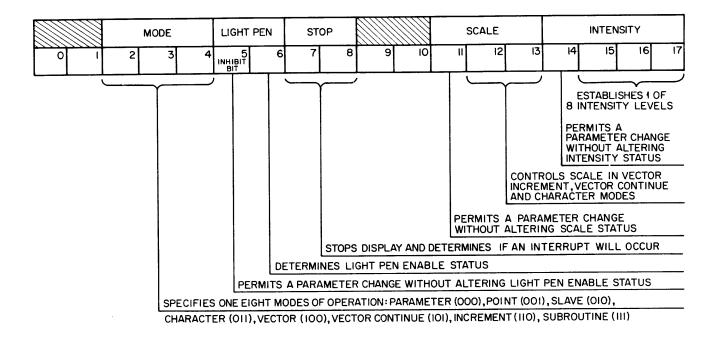

The parameter mode is specified by 0<sub>8</sub> in the mode register. This occurs when bits 2, 3, and 4 of the previous word were zero, or the escape bit was set, or an edge was violated. It also occurs when the computer issues an instruction which produces the DPY GO pulse. When in this mode, the display interprets the word in its buffer register (BR) according to the bit map in Figure 2-1.

Figure 2-1 Parameter Mode Bit Format

Bits 0 and 1 are not used. Bits 2, 3, and 4 set the mode register for the next word to be transferred. Bit 5 permits the light pen enable circuit to be set or cleared (according to bit 6) when it is a 1, and prevents the circuit from being changed when it is a 0. Bit 6 sets the LP enable flip-flop when it is a 1, and clears it when it is a 0, provided bit 5 is a 1. Bit 7 stops the display operation when it is a 1, and bit 8 generates a STOP INTERRUPT signal when it is a 1 if

bit 7 is also a 1. Bits 9 and 10 are not used. Bit 11 allows the scale register to be set and/or cleared when it is a 1, and prevents changing the register when it is a 0. Bits 12 and 13 determine the number of positions each succeeding spot is moved in the vector, vector continue, increment, and character modes. These are 1, 2, 4, or 8 positions for 00, 01, 10, or 11, respectively. Bit 14 allows the intensity register to be set and/or cleared when it is a 1, and prevents the register from being changed when it is a 0. Bits 15, 16, and 17 are loaded into the intensity register when bit 14 is a 1. These bits determine the intensity level according to their octal value, with 08 the dimmest and 78 the brightest.

### Point Mode (001)

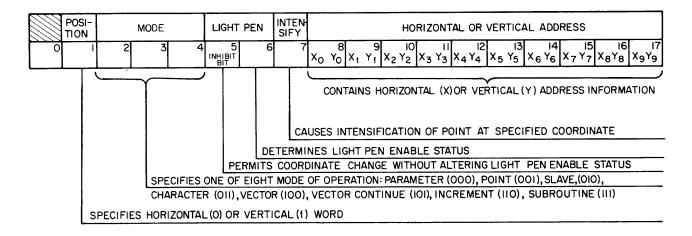

The point mode is specified by 1<sub>8</sub> in the mode register. When in this mode, the display interprets the word in its BR according to the bit map in Figure 2-2.

Figure 2-2 Point Mode Bit Format

Bit 0 is not used. Bit 1 determines the axis of the coordinate address; horizontal coordinate words are 0 and vertical coordinate words are 1. Bits 2, 3, and 4 set the mode register for the next word to be transferred. Bit 5 permits the LP enable flip-flop to be set or cleared according to bit 6. The LP enable flip-flop is set when bit 6 is a 1, and cleared when bit 6 is a 0, provided bit 5 is a 1. Bit 7 is the intensify bit, causing a spot of light to appear at the specified coordinates when it is a 1, and preventing the spot from occurring when it is a 0. Bits 8 through 17 constitute the coordinate byte. This is a 10-bit positive binary word, with zero specifying the left-hand or bottom coordinate.

### Slave Mode (010)

The display can only use the slave mode when it is equipped with the Type 343 Monitor option. The slave mode is specified by  $2_8$  in the mode register. When in this mode, the display interprets the 18-bit word in its BR according to the bit map in Figure 2-3.

Figure 2-3 Slave Mode Bit Format

Bits 0 and 1 select one of four groups of up to four slave monitor displays according to the binary value of these bits. If the display only has one group, these bits are not used. Bits 2, 3, and 4 set the mode register for the next word to be transferred. Bit 5 is not used. Bits 6 through 17 are divided into four identical 3-bit bytes, one for each of the four slave monitor displays in the group.

The most-significant bit in each byte (bits 6, 9, 12 and 15) permits the light pen and intensify control circuits to be enabled or disabled according to the other two bits when it is a 1, and prevents these circuits from being changed when it is a 0. The middle bit in each byte (bits 7, 10, 13, and 16) controls the light pen circuit when the most-significant bit is a 1. This circuit is enabled (allowing the light pen in the particular slave monitor display to generate a program interrupt signal) when the bit is a 1, and is disabled when the bit is a 0. The least-significant bit of each byte (bits 8, 11, 14, and 17) controls the intensify circuit when the most-significant bit is a 1. This circuit is enabled (allowing the picture on the Type 340 to be repeated on the particular slave monitor display) when the bit is a 1, and is disabled when the bit is a 0.

### Character Mode (011)

To use the character mode, the display must be equipped with the Type 342 Character Generator. The character mode is specified by 3<sub>8</sub> in the mode register. In this mode the display interprets all succeeding words as character words and transfers them to the Type 342. The display can only escape from the character mode when the Type 342 decodes an escape character and produces an escape pulse (or the computer issues an IOT that produces the DPY GO pulse). In either case, the mode register will be cleared, returning the display to the parameter mode.

Figure 2-4 Character Mode Bit Format

The display transfers a 6-bit byte to the character generator, which then produces a series of pulses that causes the display to plot the character point-by-point. After the character generator finishes its operation, it signals the display, which then either transfers the next byte to the character generator or generates a request for more data from the computer.

## Vector Mode (100)

The vector mode is specified by 4<sub>8</sub> in the mode register. When in this mode, the display interprets the word in its BR according to the bit map in Figure 2-5. The display remains in the vector mode until a word is transferred to it with the escape bit set or it moves a spot past the edge of the raster. Violating an edge sets the edge flag flip-flop and generates an interrupt signal that causes the computer to break its main program.

Bit 0 is the escape bit. When it is a 1, the display clears its mode register, returning to the parameter mode. Bit 1 is the intensify bit. When it is a 1, all successive points of the vector are intensified. Bits 2 through 17 consist of two 8-bit bytes. Each byte specifies the size of the vector component along one of the coordinate axis, and the direction from the starting point. Bits 2 through 9 comprise the Y component byte and bits 10 through 17 comprise the X component byte. The most-significant bit of each byte is the sign bit, with 0 signifying a positive (up or right) direction and 1 signifying a negative (down or left) direction.

The remaining 7 bits of each byte specify the number of increments the vector will be moved along the respective axis. Since this is a binary number, a maximum of 128 increments is possible. The display calculates whether or not to move the spot at each incrementing time (every 1.5 microseconds), using both bytes simultaneously. The resultant vector is straight only on vertical, horizontal, or 45° lines; however, at other angles the dot is never more than one incremental unit from a straight line. If the smallest (X1) scale is used, the incremental unit is about 2/3 the spot diameter, so the line looks straight.

Figure 2-5 Vector and Vector Continue Modes Bit Format

## Vector Continue Mode (101)

The vector continue mode is specified by 5<sub>8</sub> in the mode register. This mode is essentially the same as the vector mode and uses the same word format, shown in Figure 2-5. The only difference is that, when the vector has been drawn to the end point specified by the two component bytes, the display does not halt but continues drawing the vector at the same angle until it reaches the edge of the raster. The display then stops, requests a new word from the computer, and automatically escapes into the parameter mode. At this time the beam is located on the opposite side of the raster from where it violated the edge.

## Increment Mode (110)

The increment mode is specified by 68 in the mode register. When in this mode, the display interprets the word in the BR according to the bit map in Figure 2-6. Once the display is placed in the increment mode, it can only return to the parameter mode when it either receives a word with the escape bit set, increments beyond the edge of the raster, or receives from the computer an IOT which produces the DPY GO pulse.

Figure 2–6 Increment Mode Bit Format

Bit 0 is the escape bit. When it is a 1, the display clears the mode register, escaping to the parameter mode. Bit 1 is the intensify bit. When it is a 1, each incremental point is displayed, while the spot is moved but not displayed if it is a 0. Bits 2 through 17 consist of four 4-bit bytes, each of which specifies if and when the spot is to be moved from its previous location. The bytes are operated on separately, requiring 1.5 microseconds each. The complete word is processed in approximately 9 microseconds from the starting pulse to the next request for data signal.

## Subroutine Mode (111)

The display can only use the subroutine mode if it is equipped with a Type 347 Subroutine Interface option. The subroutine mode is specified by  $7_8$  in the mode register. When in this mode, the display interprets the word in its BR according to the bit map in Figure 2-7.

Figure 2-7 Subroutine Mode Bit Format

Bits 0 and 1 constitute the instruction part of the word. Bits 2, 3, and 4 set the mode register for the next word to be transferred. Bits 5 through 17 contain a 13-bit address, specifying a location in the computer memory.

The instruction bits are decoded to select one of three jump instructions; the fourth combination (00) is not used. These instructions are:

- 1. DDS Display Deposit Save Register. This instruction is specified by 01 in the instruction bits. It causes a word to be deposited in memory at the location specified by the 13-bit address byte and sets the mode register for the next word in the table. The DDS instruction is the return jump instruction for multilevel subroutines and is placed at the top of the subroutine table (the DJS instruction which calls this multilevel subroutine must specify the subroutine mode). The word which is transferred contains a jump instruction to the location following the DJS instruction which called the multilevel subroutine and returns the display to the parameter mode.

- 2. DJP Display Jump. This instruction is specified by 10 in the instruction bits. It causes the address contained in the address byte to be loaded into the display address counter (DAC) and sets the mode register for the next word (first word in the subroutine). The previous address held by the DAC is lost. The DJP instruction is a non-return jump to a subroutine.

- 3. DJS Display Jump and Save. This instruction is specified by 11 in the instruction bits. It causes the address contained in the address byte to be loaded into the DAC, increments and transfers the address which was in the DAC to the address save register (ASR), and sets the mode register for the next word (first word in the subroutine). In single-level subroutines, when the display escapes from the vector, vector continue, or increment modes, the address saved in the ASR is automatically transferred to the DAC, returning the program back to the location following the jump. In multilevel subroutine calls the return address saved in the ASR must be transferred to memory before any other jumps are made. This is accomplished with the DDS instruction

which precedes the other instructions in the subroutine and requires that the DJS instruction specify the subroutine mode.

#### PDP-1 PROGRAMMING

Most PDP-1/340 combinations utilize the Type 19 High Speed Channel Control and the direct access channel configuration. The IOT display load address counter (DLA, 720015) loads the display address counter (DAC) from the I/O register by a 1's transfer. DLA first clears the DAC and mode register and sets the request for data (RFD) flip-flop in the display; then it loads the DAC with the address from the I/O. During the break cycle initiated by the RFD, the address in the DAC is read into the MA, the selected word in memory is transferred to the memory buffer (MB), the DAC is incremented but the program counter (PC) is not, and the display reads the word from the MB into its buffer register (BR). Since the display is in the parameter mode (because the mode register was cleared), it sets various control flip-flops as specified by the information in the word and also sets the RFD flip-flop to generate another break cycle if the stop bit is not set. This operation occurs before the computer has finished its break cycle; so unless the stop bit has been set, the next computer cycle is another break cycle.

During this second cycle the computer transfers the second word from the table to the display, which interprets it in one of the operating modes determined by the mode bits of the preceding parameter word. This word is generally a point mode word containing the Y, or vertical, co-ordinate address. The word is loaded into the BR in the usual manner. The coordinate address is then transferred into the Y register, and finally the RFD flip-flop is set to request another word. (This occurs before the PDP-1 finishes its break cycle.) A third break cycle then occurs, in which the computer transfers another point mode word containing the X, or horizontal, co-ordinate address. When this coordinate is loaded into the X register, it initiates a 35-microsecond delay. During this time, the computer is freed to continue its main program. At the end of the 35 microseconds, a spot of light appears if the intensify bit has been set, and the RFD flip-flop is set to request another break cycle.

The next word will probably be an increment, vector, vector continue, or character mode word, depending on the mode bits of the last point mode word. If this is the case, the display performs the required operation and requests another break cycle when it is done, but does not

clear the mode register (unless the escape bit is set or an edge is violated). Each succeeding word is interpreted as being in the same mode. When the display is in the increment, vector, or vector continue modes and receives a word with the escape bit set, it clears the mode register when it requests another break cycle; so the next word is interpreted in the parameter mode. If the display is in the character mode, the character generator produces an escape pulse (when it encounters an escape character) which also clears the mode register. During the display operations, which can last as long as 1.5 milliseconds, the computer is free to continue with its main program.

The last word in a series of display operations must be a parameter word in order to stop the display. When the stop bit is set in this word, the stop flip-flop is set. The interrupt bit of this word must also be set to generate an interrupt signal, as no RFD is generated.

If the Type 370 Light Pen is being used and sees a spot of light, it stops the X and Y registers from being loaded or the other modes from continuing, preventing the RFD flip-flop from being set. The display halts its operations and produces a light pen flag signal for the computer, causing a program interrupt. The computer jumps to a subroutine to service the interrupt and then issues the IOT display resume sequence (DRS, 720115), which clears the light pen flip-flops and allows the display to finish the interrupted operation.

The IOT instructions which control the operation of the PDP-1/340 system are listed in Table 2-1. (The octal values of these instructions may be different for some computers.) These instructions can be microprogrammed (combined) by adding the center two octal digits of two or more listed instructions to make a new instruction. The last two digits of each instruction used in microprogramming must always be the same (as must the first two). Example: DSE (display skip on edge violation, 721417) is the combination of DSV and DSH.

TABLE 2-1 TYPICAL PDP-1 IOT DISPLAY INSTRUCTIONS

| Mnemonic | Octal Value              | Name/Explanation                                                                           |

|----------|--------------------------|--------------------------------------------------------------------------------------------|

| DLA      | 720015 7779775<br>720025 | Display Load Address Counter<br>/C(IO) ⇒ C(DAC), DPY GO starts the dis-<br>play operation. |

TABLE 2-1 TYPICAL PDP-1 IOT DISPLAY INSTRUCTIONS (continued)

| Mnemonic | Octal Value                            | Name/Explanation                                                                                                                                             |

|----------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRS      | 720115 <b>720125</b>                   | Display Resume Sequence /Clears light pen flag and restarts the in- terrupted display operation.                                                             |

| DCF      | 720215 <b>720225</b>                   | Display Clear Flags<br>/Clears the light pen, edge violation, and re-<br>quest for data flags.                                                               |

| DRA      | 720016 <b>720026</b>                   | Display Read Address Counter<br>/C(DAC) ⇒ C(IO).                                                                                                             |

| DRC      | 720116 <b>17297719</b><br>720126       | Display Read Coordinates $/C(X_{0-8}) \Rightarrow C(IO_{0-8}), C(Y_{0-8}) \Rightarrow C(IO_{9-17}).$                                                         |

| DSP      | 720117 <b>720127</b><br>720127         | Display Skip on Light Pen Flag<br>/C(PC) + 1 ⇒ C(PC) if LP FLAG occurs.                                                                                      |

| DSS      | 720217 <b>740947</b><br>72022 <b>7</b> | Display Skip on Stop Interrupt<br>/C(PC) + 1 ⇒ C(PC) if stop interrupt occurs.                                                                               |

| DSV      | 720417 <b>7254777</b><br><b>720427</b> | Display Skip on Vertical Edge Violation $/C(PC) + 1 \Rightarrow C(PC)$ if spot moves past top edge. Interrupt will occur except in vector continue mode.     |

| DSH      | 721017 <b>7448477</b><br><b>721027</b> | Display Skip on Horizontal Edge Violation $/C(PC) + 1 \Rightarrow C(PC)$ if spot moves past right edge. Interrupt will occur except in vector continue mode. |

## PDP-4 AND PDP-7 PROGRAMMING

Both the PDP-4 and the PDP-7 computers use the same symbolic and machine language, and perform the same functions. The primary difference between the two computers is their memory cycle time: the PDP-4 requires 8 microseconds, while the PDP-7 requires only 1.75 microseconds (this can be slowed to 3.75 microseconds for slow-speed information transfer). Most installations use the 4,096 or 8.192 word core memories, requiring a 13-bit display address counter (DAC) in the direct access channel option. However, any extended memory system requires a 15-bit DAC.

If the Type 340 is the only peripheral device requiring direct access to the memory of the computer, the real time control provides the necessary access when using a DAC. However, if additional options also require direct memory access, a Type 133 Data Interrupt Multiplexer is required. Both the real time control and the data interrupt multiplexer allow the display to have access to memory via a break cycle in the same fashion as that described for the PDP-1. In the case of the PDP-7, the data break occurs at the slow (3.75 microsecond) memory cycle speed.

The mnemonics of the symbolic language are mainly the same as for the PDP-1. However, the octal values of the machine language are different. These are listed in Table 2-2. As with the PDP-1, microprogramming is possible by combining two or more IOT's that differ only in the least-significant octal bit.

TABLE 2-2 PDP-4 AND PDP-7 DISPLAY IOT'S

| Mnemonic | Octal Value | Name/Explanation                                                                                         |

|----------|-------------|----------------------------------------------------------------------------------------------------------|

| DSE      | 700501      | Display Skip on Edge Violation  /C(PC) + 1 ⇒ C(PC) when an edge flag occurs.                             |

| DRA      | 700502      | Display Read Address Counter<br>/C(DAC) ⇒ C(AC).                                                         |

| DRS      | 700504      | Display Resume Sequence /Clears light pen flag and restarts the inter- rupted display operation.         |

| DSI      | 700601      | Display Skip on Stop Interrupt /C(PC) + 1 ⇒ C(PC) if a stop interrupt occurs.                            |

| DCA      | 700602      | Display Clear Address Counter /0 ⇒ C(DAC).                                                               |

| DLA      | 700604      | Display Load Address Counter<br>/C(AC) ⇒ C(DAC), DPY GO starts the dis-<br>play operation.               |

| DSP      | 700701      | Display Skip on Light Pen Flag $/C(PC) + 1 \Rightarrow C(PC)$ if a light pen flag has occurred.          |

| DRC      | 700702      | Display Read Coordinates $/C(X_{0-8}) \Rightarrow C(AC_{0-8})$ , $C(Y_{0-8}) \Rightarrow C(AC_{9-17})$ . |

| DCF      | 700704      | Display Clear Flags/Clear light pen, edge violation, and request for data flags.                         |

#### PDP-6 PROGRAMMING

All 340 Displays operated by a PDP-6 require a 344 Interface. This interface stores the 36-bit data word from the PDP-6 and applies it as two 18-bit words to the 340 when requested. (The left half of the word is always used before the right half.) The 344 also contains the logic circuits which produce the required control signals, interrupt and flag signals, and coordinate register status signals.

Normally the PDP-6 operates the 340 in the priority interrupt mode, although this is not necessary when no other time demands are made on the computer. Two different priority interrupt channels are used by the 340 because of the two types of conditions under which the display stops operating. One channel is used to request a new data word when the display transfers the second half of the word in the interface buffer (IB) into its buffer register (BR) and commences its second operating cycle. The other channel generates an interrupt signal when any of the special display stop conditions occur; i.e., the light pen has seen a spot, an edge has been violated (except in the vector continue mode), or the stop bit was set.

When using the priority interrupt mode, one or two priority interrupt channels in the computer must first be turned on. This is accomplished with the CONO instruction to the priority interrupt system (PI) according to the bit map shown in Figure 2-8.

Figure 2-8 Priority Interrupt System Bit Format

The same channels must then be assigned to the display. This is accomplished with a CONO instruction to the display (DIS), as shown by the bit map in Figure 2-9. In this case, bits 30, 31, and 32 specify the octal number of the special priority interrupt channel, and bits 33, 34, and 35 specify the octal number of the data priority interrupt channel. When the initialize bit (29) is set, the done flag is set and a data interrupt request generated, and the DPY GO pulse is produced and applied to the display, clearing the light pen flag circuit and stop flip-flop and generating a request for data signal. The CONO instruction always produces the RESUME pulse, to clear the light pen flag flip-flops, and restarts the interrupted instruction (except in the character mode) unless bit 29 is set.

Figure 2-9 Display Interface Conditions Bit Format

When the computer grants an interrupt request, it executes the instruction contained in location 40 + 2J (where J is the number of the priority interrupt channel) without incrementing the program counter. As long as this instruction does not change the program counter, the computer will resume its program at the point where the interrupt occurred. However, if it is a jump or similar instruction that does change the program counter, some means must be provided to return the program to its interrupted location.

Normally the instruction in location 40 + 2J will be a jump to subroutine, JSR or a BLKO. In the case of the JSR the PDP-6 processor first calculates the effective address, then stores the

counter (which has been incremented and points to the next instruction in the normal sequence) in the right half of the effective address; and lastly jumps to the effective address + 1. This is the beginning of a subroutine that services the interrupt. At or near the end of this subroutine must be a JRST or CONO instruction to dismiss the priority interrupt channel; otherwise no interruptions can occur from lower or equal priority interrupt channels if they exist. The last entry in the subroutine may be a jump and restore (JRST) instruction that jumps indirectly back to the first address in the subroutine. In this location are stored the contents of the flags and program counter, so the program resumes at the location specified in the right half of this word. The JRST instruction must have the number 12 in its accumulator field to dismiss the priority interrupt channel and restore the flags and program counter.

The BLKO instruction is used to transmit a block of data words, one word at a time to the interface for use by the display. This instruction goes to its effective address to pick up a pointer word. In the left half of the pointer word is the negative of the number of words in the table, and in the right half of the word is the location -1 of the beginning of the table. This pointer word is retrieved from memory and each half incremented by one. The computer then fetches the word specified by the address in the right half of the pointer word, places it on the I/O bus, and produces the DATAO CLEAR and DATAO SET pulses to transfer this word to the display. At the same time, the left half of the pointer word is tested for a zero to determine the next action. If the left half is zero (end of block condition), the computer next executes the instruction in location 41 + 2J (without disturbing the program counter). This instruction must be a JSR to a subroutine that will dismiss the priority interrupt channel and return the computer to its interrupted program location and may reset the pointer. If the left half of the pointer word is not zero, the priority interrupt channel is automatically dismissed and the computer returns to its normal program at the location specified by the program counter.

The DATAO instruction transfers just the one word specified by the effective address to the interface buffer. The DATAI instruction transfers the X and Y coordinates to the location specified by the effective address. The Y coordinate is contained in bits 8 through 17 (right justified in the left half of the word), and the X coordinate is contained in bits 26 through 35 (right justified in the right half of the word).

Either the CONI, CONSZ, or CONSO instruction will transfer the current states of the flag and priority interrupt flip-flops to the effective address. These are located in bits 24 through 34 (except 29) as shown in Figure 2-9. The CONSZ and CONSO instructions test these bits against a mask in the effective address. If all the bits in the mask which are ones match the ones in the flag and interrupt bits, the CONSO executes the next instruction in sequence while the CONSZ skips this instruction and executes the second instruction in sequence. However, if any mask bit which is a one coincides with a zero in the flag and interrupt bits, the CONSZ executes the next instruction while the CONSO skips this and executes the second instruction.

A demonstration program is listed in Table 2-3. This program continously draws the figure 4B in the lower right corner of the raster. If the light pen sees any part of the figure except the lower left dot of the B, the program halts until the I/O RESET key is depressed. If this particular dot is seen by the light pen, the display gets brighter and the computer halts. If the figure violates an edge of the raster, the display moves until no violation occurs.

This program is written for the MACRO6 Assembler. All numbers are octal (radix 8). If many increment modes words are used, they can be coded easier in numbers to the radix 4, (see Figure 2-6). Notice that the first word (left half) in the last data table entry stops the display and generates a new data interrupt. Since the first data interrupt has not yet been dismissed, the computer does another BLKO instruction, sees that the left half of the pointer word is zero, and enters the REPEAT subroutine. This renews the pointer word and dismisses the interrupt channel, at which time the second data interrupt is entered and the display cycle repeats itself.

If the display data table is to be changed or modified, thus varying its length, the last word in the table should be 003000<sub>8</sub>, which would halt the display, set the stop flag, and generate a special interrupt request. The stop flag subroutine must then renew the pointer word. The table length then becomes independent of the pointer word as long as it does not exceed the value specified.

TABLE 2-3 TYPICAL PDP-6 PROGRAMMING EXAMPLES

| Location : | Instruction AC ,                                                                                                     | Address (Index)                                                                        | ; Comments                                                                                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                                                                                      | 2202                                                                                   | ACCIONIC ANID TURNIC ON DI CHANINITIC /                                                                                                                                                                                                                                                   |

|            | CONO PI,                                                                                                             | 2203                                                                                   | ; ASSIGNS AND TURNS ON PI CHANNELS 6<br>; AND 7.                                                                                                                                                                                                                                          |

|            | CONO DIS,                                                                                                            | 167                                                                                    | ; ASSIGNS PI CHANNELS 6 AND 7 TODISPLAY<br>; SETS DONE FLAG AND GENERATES DATA IN<br>; TERRUPT ON PI CHANNEL 7.                                                                                                                                                                           |

| LOC 54 :   | JSR ,                                                                                                                | WHY                                                                                    | ; SPECIAL INTERRUPT SUBROUTINE. ; NOT USED.                                                                                                                                                                                                                                               |

| LOC 56 :   | BLKO DIS,                                                                                                            | TABLE<br>REPEAT                                                                        | ; DATA INTERRUPT, TRANSFERS 1 WORD.<br>; JUMP TO RESTORE POINTER WORD.                                                                                                                                                                                                                    |

| TABLE :    | XWD 103760,<br>XWD 140000,<br>XWD 325063,<br>XWD 100000,<br>XWD 140000,<br>XWD 231673,<br>XWD 100000,<br>XWD 600203, | 220000<br>703100<br>304210<br>631777<br>600210<br>237463<br>704210<br>203400<br>140000 | ; POINTER WORD. ; SETS PARAMETERS, Y AXIS. ; SETS X AXIS, DRAWS LINE. ; SETS MODE, DRAWS CURVE. ; DRAWS CURVE. ; SETS MODE, DRAWS LINE. ; SETS MODE, DRAWS CURVE. ; DRAWS CURVE. ; SETS MODE, DRAWS LINE. ; DRAWS LINE, SETS MODE.                                                        |

|            | =                                                                                                                    | 631273<br>000000                                                                       | ; DRAWS CURVE.<br>; STOPS, SETS DONE FLAG, GENERATES DATA<br>; INTERRUPT.                                                                                                                                                                                                                 |

| REPEAT :   | MOVE 0,<br>MOVEM 0,<br>JRST 12,                                                                                      | TABLE<br>@3                                                                            | ; BLANK TO STORE FLAGS AND PC.<br>; FETCH POINTER WORD.<br>; RENEW POINTER WORD.<br>; DISMISSES PI CHANNEL, RESTORES FLAGS<br>; AND PC.                                                                                                                                                   |

| POINT :    | XWD -13,                                                                                                             | TABLE                                                                                  | ; POINTER WORD FOR DATA INTERRUPT.                                                                                                                                                                                                                                                        |

| WHY:       | CONSZ DIS, JSR , CONSZ DIS, JSR , CONSZ DIS, JSR , CONSZ DIS,                                                        | 2000<br>LPFLAG<br>1000<br>HFLAG<br>4000<br>VFLAG<br>400<br>STOP                        | ; BLANK TO STORE FLAGS AND PC. ; TEST FOR LIGHT PEN INTERRUPT. ; JUMP IF LP FLAG IS SET. ; TEST FOR HORIZONTAL EDGE VIOLATION. ; JUMP IF HOR EDGE FLAG IS SET. ; TEST FOR VERTICAL EDGE VIOLATION. ; JUMP IF VER EDGE FLAG IS SET. ; TEST FOR STOP INTERRUPT. ; JUMP IF STOP FLAG IS SET. |

TABLE 2-3 TYPICAL PDP-6 PROGRAMMING EXAMPLES (continued)

| Location : | Instruction | AC , Address (Index) | ; Comments                                          |

|------------|-------------|----------------------|-----------------------------------------------------|

|            | JRST        | 12,@WHY              | ; JUMP INDIRECT TO WHY, RESTORE FLAGS               |

|            |             |                      | ; AND PC, AND DISMISS PI CHANNEL.                   |

| LPFLAG :   | <br>7       | ••••                 | ; BLANK TO STORE FLAGS AND PC.                      |

| LITEAU .   | CONO        | DIS, 67              | ; COMPLETES DISPLAY.                                |

|            | JSR         | , SAVEAC             | ; JUMP TO SUBROUTINE, THEN RETURN.                  |

|            | DATAI       | DIS, STORE           | ; STORE X AND Y COORDINATES.                        |

|            | HLRZ        | 2, STORE             | ; Y COORDINATE TO AC2, SWAPPED.                     |

|            | TRINE       | 2, 1777              | ; TEST FOR BOTTOM EDGE OF RASTER.                   |

|            | JRST        | , HOLD               | ; JUMP IF NOT BOTTOM EDGE.                          |

|            | HRRZ        | 2, STORE             | ; X COORDINATE TO AC2.                              |

|            | TRNE        | 2, 1003              | ; TEST FOR VERTICAL BAR.                            |

|            | JRST        | , HOLD               | ; JUMP IF NOT VERTICAL BAR.                         |

|            | MOVS        | 3, TABLE+1           | ; RETRIEVE PARAMETER WORD, SWAPPED.                 |

|            | ADDI        | 3, 1601              | ; INCREMENTS INTENSITY, SETS DONE                   |

|            |             |                      | ; FLAG AFTER SECOND TIME.                           |

|            | MOVSM       | 3, TABLE+1           | ; REPLACE PARAMETER WORD, SWAPPED.                  |

|            | JSR         | , RSTAC              | ; JUMP TO SUBROUTINE, THEN RETURN.                  |

|            | JRST        | 2, @LPFLAG           | ; JUMPS INDIRECT TO LPFLAG, RESTORES                |

|            |             |                      | ; FLAGS AND PC.                                     |

| HOLD :     | : JRST      | 4,2                  | ; HALTS UNTIL I/O RESET KEY IS DEPRESSED,           |

| STOPE      | 7           |                      | ; THEN RESUMES.                                     |

| STORE :    | : Z         |                      | ; BLANK TO STORE X AND Y COORDINATES                |

| HFLAG :    |             | • • • •              | ; BLANK TO STORE FLAGS AND PC.                      |

| HELAG      | : ∠<br>JSR  | , SAVEAC             | ; JUMP TO SUBROUTINE, THEN RETURN.                  |

|            | MOVS        | 3, TABLE+2           | ; RETRIEVE PARAMETER WORD, SWAPPED.                 |

|            | ADDI        | 3, 1                 | ; INCREMENT X COORDINATE.                           |

|            | MOVSM       | 3, TABLE+2           | ; REPLACE PARAMETER WORD, SWAPPED.                  |

|            | JSR         | , RSTAC              | ; JUMP TO SUBROUTINE, THEN RETURN.                  |

|            | JRST        | 2, @HFLAG            | ; JUMPS INDIRECT TO HFLAG, RESTORES                 |

|            | JIGT        | 2, 61112710          | ; FLAGS AND PC.                                     |

|            | <u></u>     | ••••                 |                                                     |

| VFLAG      |             |                      | ; BLANK TO STORE FLAGS AND PC.                      |

|            | JSR         | , SAVEAC             | ; JUMP TO SUBROUTINE, THEN RETURN.                  |

|            | HRR         | 3, TABLE+1           | ; Y COORDINATE RETRIEVED.                           |

|            | ADDI        | 3, 1                 | ; INCREMENT Y COORDINATE.                           |

|            | HRRM        | 3, TABLE+1           | ; REPLACES Y COORDINATE.                            |

|            | JSR         | , RSTAC              | ; JUMP TO SUBROUTINE, THEN RETURN.                  |

|            | JRST        | 2,@VFLAG             | ; JUMPS INDIRECT TO VFLAG, RESTORES ; FLAGS AND PC. |

|            |             |                      | , 12103 AND 10.                                     |

|            |             |                      |                                                     |

TABLE 2-3 TYPICAL PDP-6 PROGRAMMING EXAMPLES (continued)

| Location : Instruction                                  | AC , Address (Index                                                | x); Comments                                                                                                                                                                                                                                |

|---------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP : Z<br>JRST                                        | 16, @STOP                                                          | ; BLANK TO STORE FLAGS AND PC.<br>; RESTORES FLAGS AND PC, DISMISSES<br>; INTERRUPT, AND HALTS.                                                                                                                                             |

| SAVEAC : Z  MOVEM  MCVE  BLT  JRST  XWD  ACCMTB : BLOCK | 0, ACCMTB<br>0, .+3<br>0, ACCMTB+17<br>2, @SAVEAC<br>1, .+2<br>20, | ; BLANK TO STORE FLAGS AND PC. ; STORE ACO IN TABLE. ; FETCH BLOCK DESIGNATOR WORD. ; STORE ACCUMULATORS. ; JUMP INDIRECT TO SAVEAC, RESTORE ; FLAGS AND PC. ; BLOCK DESIGNATOR WORD. ; SIXTEEN BLANK LOCATIONS TO STORE ; ACCUMULATORS IN. |

| RSTAC : Z  MOVE BLT JRST  XWD ACC                       | <br>17, .+3<br>17, 17<br>2,@RSTAC<br>CMTB, 0                       | ; BLANK TO STORE FLAGS AND PC. ; FETCH BLOCK DESIGNATOR WORD. ; RESTORE ACCUMULATORS. ; JUMP INDIRECT TO RSTAC, RESTORE ; FLAGS AND PC. ; BLOCK DESIGNATOR WORD.                                                                            |

### SECTION 3

#### LOGICAL OPERATION

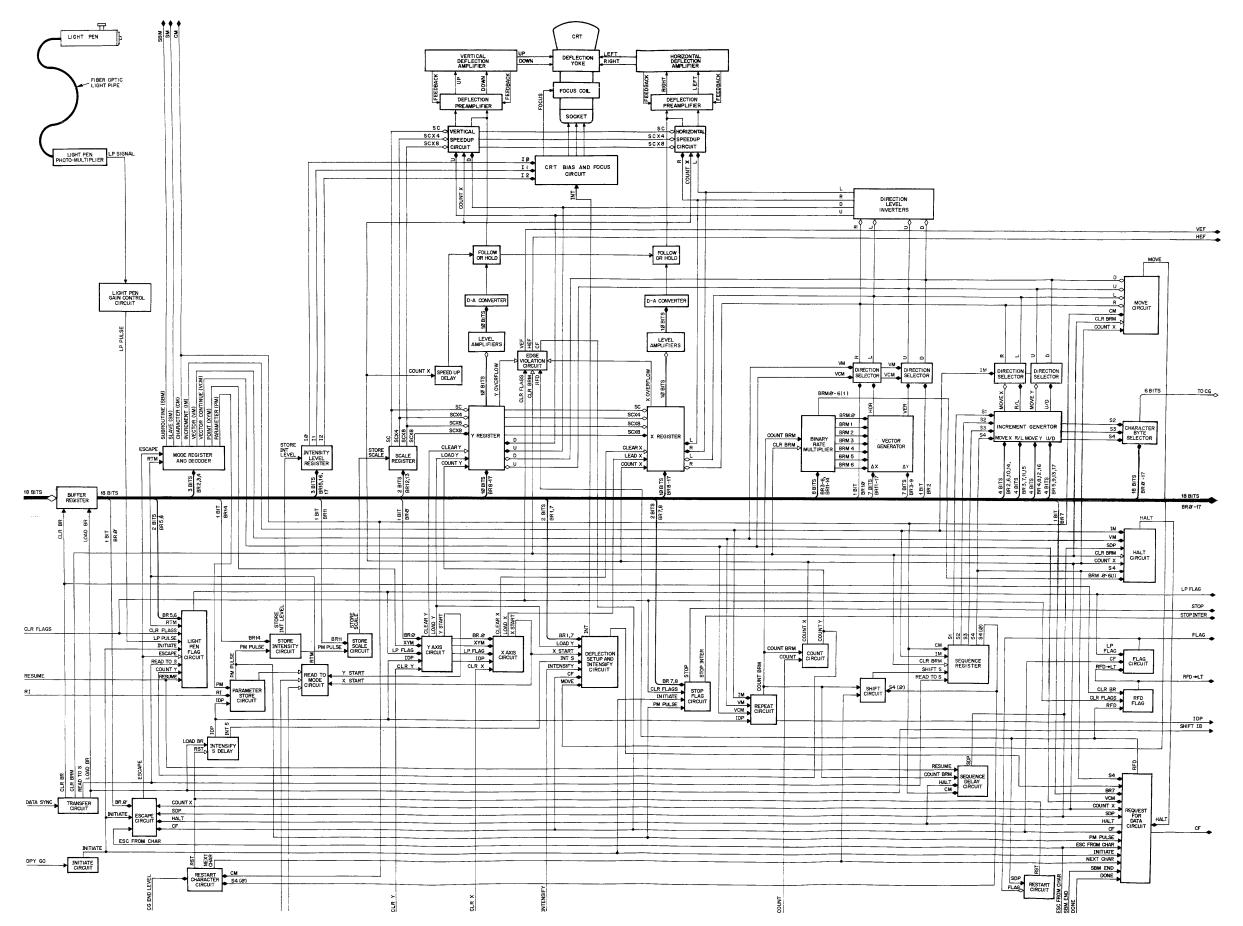

The Type 340 operates as a small, special purpose, stored program computer. It uses part of the memory in its controlling computer to store its program, performs the instruction contained in this memory in a step by step sequence, calculates the hypotenuse of a right triangle in the vector and vector continue modes, and is capable of jumping to subroutines in the subroutine mode. In order to understand the operation of the display, it is necessary first to know what the display does in each of its modes, and then to follow the path of a signal through the display's circuits in these modes. This can best be accomplished with the signal flow diagram shown in Figure 3-1.

### SIGNAL FLOW

## Initial Starting

The Type 340 is turned on either by throwing the switch on the power control panel to ON or by the computer supplying a -15 volt remote turn on signal. When this occurs, power is immediately available for the logic circuits, but the CRT and its ultor voltage power supply require a few seconds warmup time. Initially the flip-flops are arbitrarily set, but this does not affect most of the registers as they are cleared before they are loaded. However, some of the control flip-flops must be preset before the display can begin normal operation. This is accomplished with the IOT display load address counter, DLA, if a PDP 1, PDP 4, or PDP 7 is used, or the CONO DIS 0001XY if the PDP 6 is used. These instructions produces the DPY GO pulse.

This pulse, shown on the lower part of Figure 3-1, clears the 3-bit mode register, the three light pen flip-flops, and the stop flip-flop. It also generates the RFD pulse which clears the two edge flag flip-flops (HEF and VEF) and sets the RFD flip-flop, generating the RFD — LT level which requests a data word from the computer. When the computer grants this request, the first word is interpreted in the parameter mode and sets up the parameter flip-flops according to the information contained in it.

#### Parameter Mode

When the three mode flip-flops hold the octal number 0, the next word loaded into the buffer register is interpreted in the parameter mode. The information in this word sets the mode register flip-flops to the mode for the next word and may set the stop flip-flop, generate a STOP INTERRUPT signal, and set or clear the light pen enabling flip-flop, the scale register flip-flops, and the intensity register flip-flops. The parameter word bit map is shown in Figure 2-1.

The computer issues a DATA SYNC pulse either just before or when the requested 18-bit data word is available on the input cable. This pulse, shown at the top left of Figure 3-1, starts the display's operation. It generates the CLR BR pulse which (1) clears the buffer register (BR) and the RFD flip-flops; (2) produces the CRL BRM pulse that clears the binary rate multiplier (BRM), sequence register (S), the two edge flag flip-flops (HEF and VEF), and the halt and move flip-flops; and (3) initiates a 2.8-microsecond setup delay. This delay allows the input word time to set up the readin gates to the BR and for the carries in the BRM to die out.

At the end of the setup delay period a READ TO S pulse is produced. This pulse sets the LP flag flip-flop if the light pen is enabled and saw a spot during the last display operation.

The READ TO S pulse also generates the LOAD BR and SHIFT-IB pulses and initiates an 0.5-microsecond intensify s delay. The LOAD BR pulse transfers those bits of the input word which are logic ones to the buffer register. The SHIFT-IB pulse is only used with the PDP 6, and it shifts the right-half of the interface buffer (IB) into the left half with a jent transfer. The 0.5-microsecond delay allows time for the BR to be loaded and its output to stabilize, but the duration is set as the spot intenisfication time when in the increment, vector, or vector continue modes. At the end of this delay an intensify delay pulse (IDP) is produced. The display now chooses how it will interpret the word in its BR.

Since this is the parameter mode, a READ TO MODE pulse and a parameter mode pulse (PM PULSE) are produced. The READ TO MODE pulse loads the 3-bit mode register with the contents of BR2, BR3, and BR4, setting the mode for the next word. If BR5 is a 1, the READ TO MODE pulse sets or clears the light pen enable (LP enable) flip-flop, according to BR6. LP enable is set when BR6 is a 1 and is cleared when BR6 is a 0.

Figure 3–1 Flow Diagram

The PM PULSE performs various functions, depending on the states of BR7, BR8, BR11, and BR14. If another data break or word is needed, BR7 is a 0 and allows the RFD pulse to be generated. This pulse clears the two edge flag flip-flops and sets the RFD flip-flop, generating the request for data signal. If BR7 is a 1, the stop flip-flop is set and no data request is generated, stopping the display's operation. If BR8 is also a 1, a STOP INTERRUPT signal is produced, generating an interrupt request for the computer. When BR11 is a 1, a STORE SCALE pulse is produced which loads the 2-bit scale register (SZ) with the contents of BR12 and BR13. When BR14 is a 1, a STORE INT. LEVEL pulse is produced that loads the 3-bit intensity level register (I) with the contents of BR15, BR16, and BR17.

When the stop flip-flop is set and the display halts, the computer must restart operation by either another display load address counter IOT or by issuing another word and a DATA SYNC pulse after the IOT display clear flags, DCF.

### Point Mode

When the display is in the point mode, it sets the horizontal (X) and vertical (Y) registers to the coordinates of the spot location. This requires two word transfers, one for each coordinate. Since magnetic deflection is used, a 35-microsecond set up time is required before the spot can be intensified. Either word transfer can intensify the spot if desired, or this can be the starting location of a line, curve, or character specified by the next word(s) to be transferred.

Operation in the point mode only occurs if the previous word (either a parameter, point, slave, or a subroutine) had set the mode register to 001 (1<sub>8</sub>). When the display has been placed in the point, or XY, mode it interprets the 18-bit word according to Figure 2-2. The series of events from the setting of the RFD flip-flop to the generation of the IDP pulse is the same as described for the parameter mode. At this point, provided the light pen flag is not set, the display examines the state of BR1. When BR1 is a 0, the display interprets the word as a horizontal point word and generates an X START pulse; and when BR1 is a 1, the display interprets the word as a vertical point word and generates a Y START pulse. If the LP flag is set, the display halts.

Either an X START pulse or a Y START pulse will generate the READ TO MODE pulse, loading the mode register with the contents of BR2, BR3, and BR4 for the next word's mode. The X START pulse

also generates a CLEAR X pulse and initiates a 35-microsecond delay. This is the deflection setup delay, allowing the deflection currents to stabilize at their final value before the spot is intensified. The CLEAR X pulse clears the X register and, 0.2-microseconds later, generates a LOAD X pulse which loads the X register with those bits in BR8 through BR17 which are ones. The Y START pulse also generates a CLEAR Y pulse which clears the Y register and, 0.2-microseconds later, generates a LOAD Y pulse which loads the Y register with those bits in BR8 through BR17 which are ones.

At this point the display examines the intensify bit, BR7. If this bit is a 0, the LOAD Y pulse initiates an 0.5-microsecond intensify p delay. (This is the intensify delay for the point mode.) At the end of this delay the RFD pulse is produced, clearing the two edge flag flip-flops and setting the RFD flip-flop, but not intensifying the spot.

However, if BR7 is a 1, the LOAD Y pulse will initiate the 35-microsecond delay. When this deflection setup time is over, the 0.5-microsecond intensify p delay is initiated. During this period an INT signal is produced which unblanks the CRT and produces a spot of light at the coordinates specified by the X and Y registers. When the intensify delay is over, the RFD pulse is produced and the display halts with a request for data generated.

NOTE: The X point mode always produces the 35-microsecond deflection setup delay, whether or not the intensify bit is set; while the Y point mode only produces the 35-microsecond deflection delay if the intensify bit is set. Therefore the Y axis should precede the X axis when both axes are loaded to avoid an unnecessary delay.

## Light Pen Interrupt

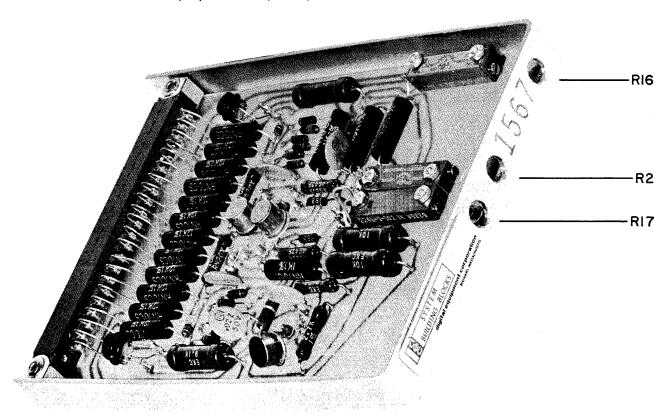

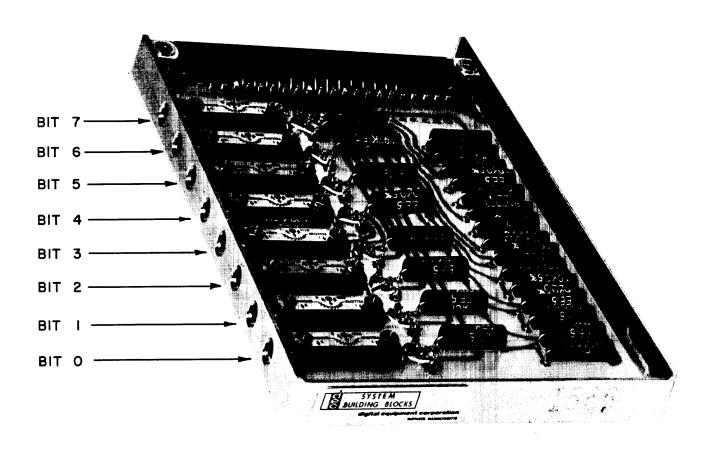

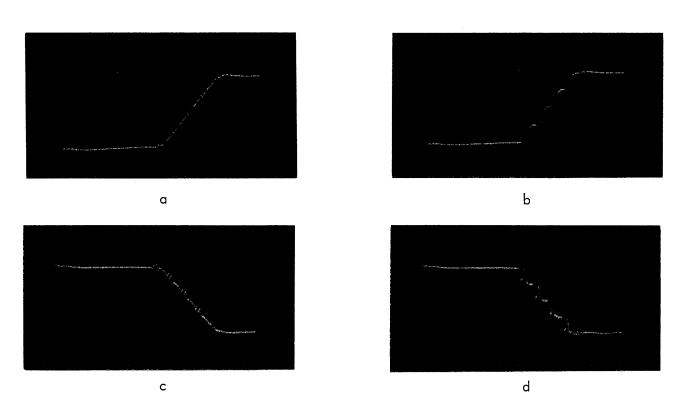

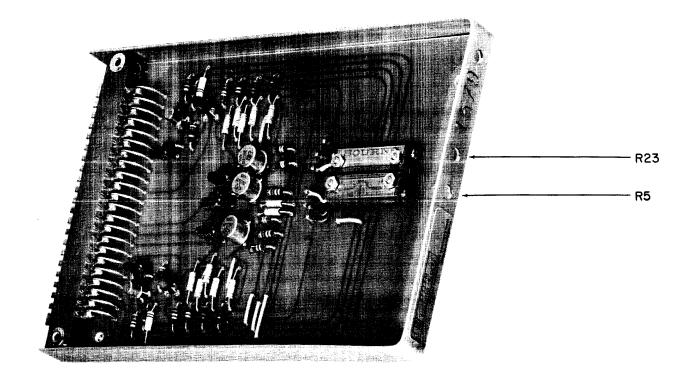

If the point mode operation is halted by the light pen seeing the previous spot, the IDP pulse will not produce an X START or Y START pulse. The computer can issue an instruction which produces the RESUME pulse in order for the display to complete its operation. (This is the IOT display resume, DRS.) for the PDP-1, PDP-4, or PDP-7 and the CONO DIS 000 0XX for the PDP 6.)